一、基本双稳态电路

1. 双稳态的概念

1.1 时序逻辑电路

时序逻辑电路的工作特点是任意时刻的输出状态不仅与当前的输入信号有关而且与此前电路的状态的电路。即具有记忆功能

锁存器和触发器是构成时序逻辑电路的基本逻辑单元

1.2 双稳态

电路内部存在且只存在两种可以长期保持的稳定状态,称这种电路为「双稳态电路」。双稳态电路在外部作用下,可从一个稳态变化到另一稳态。显然,双稳态电路具有记忆 1 位二进制数据的功能。

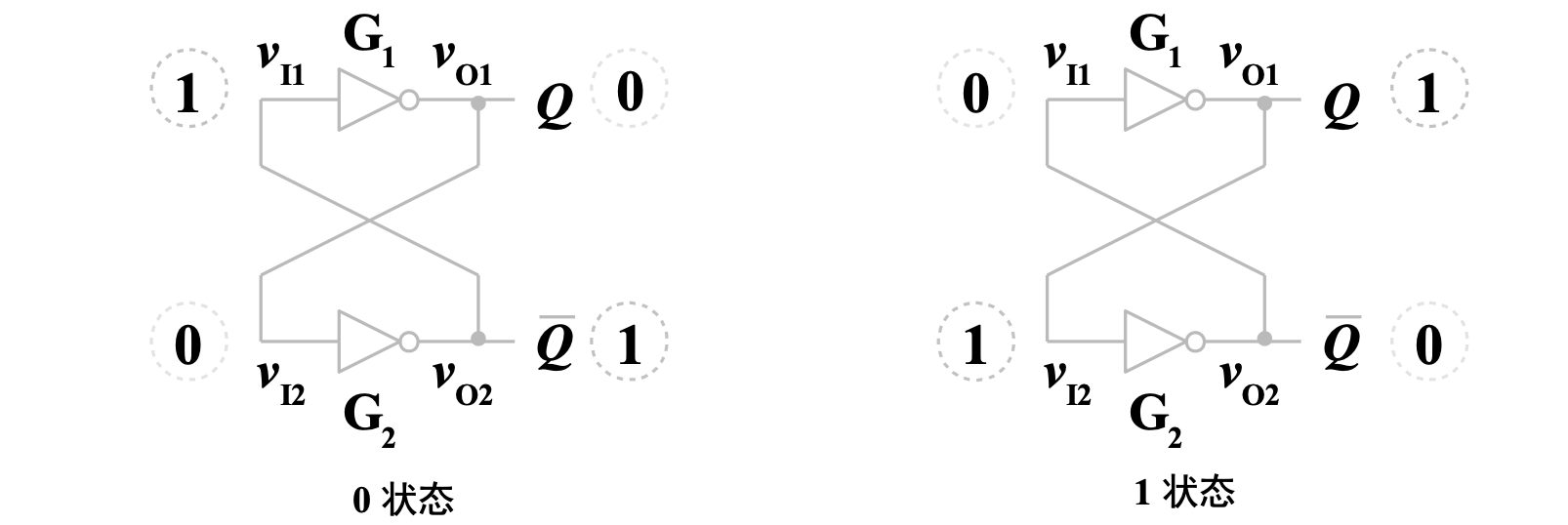

如图所示电路由两个非门组成,只存在两种稳态,且可以互相转换,这就是最简单的双稳态电路。

1.3 现态与次态

对于双稳态电路组成的电路,我们称当前的稳态为「现态」,用

在当前状态基础上,外界信号输入之后的状态称为「次态」,用

时序逻辑电路的次态不仅取决于输入信号,也取决于现态。因此可以用方程式来表示次态,如

1.4 功能表

类似真值表,可以用表格描述次态与现态和输入信号的关系,如下表为 RS 锁存器的功能表

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 |

2. 锁存器和触发器

根据双稳态电路的原理,可以设计出专门用于存储信号的电路单元,即锁存器和触发器。根据改变稳态的输入类型,可以分为锁存器和触发器。

3.1 锁存器

对脉冲电平敏感的存储单元电路称为「锁存器」(Latch),它可以在特定输入脉冲电平作用下改变状态

常用的锁存器有 SR 锁存器和 D 锁存器

3.2 触发器

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。

在时钟信号触发时才能动作的存储单元电路称为「触发器」

二、SR 锁存器

1. 基本 SR 锁存器

1.1 基本结构

SR 锁存器是最基本的锁存器之一,由两个或非门组成,如图

SR 锁存器有两个互补的输出端

- R-Reset 为置 0 端,即复位端

- S-Set 为置 1 端,即置位端

SR 锁存器的次态方程式可以表示为

1.2 工作原理

当

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

此时输入为无效信号,状态保持。

当

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 |

此时

当

| 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 |

此时

当

| 0 | 0 | 1 | ? |

| 1 | 0 | 1 | ? |

RS 锁存器的功能表还可以表示为

| 0 | 0 | Q |

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 1 | ? |

1.3 动态特性

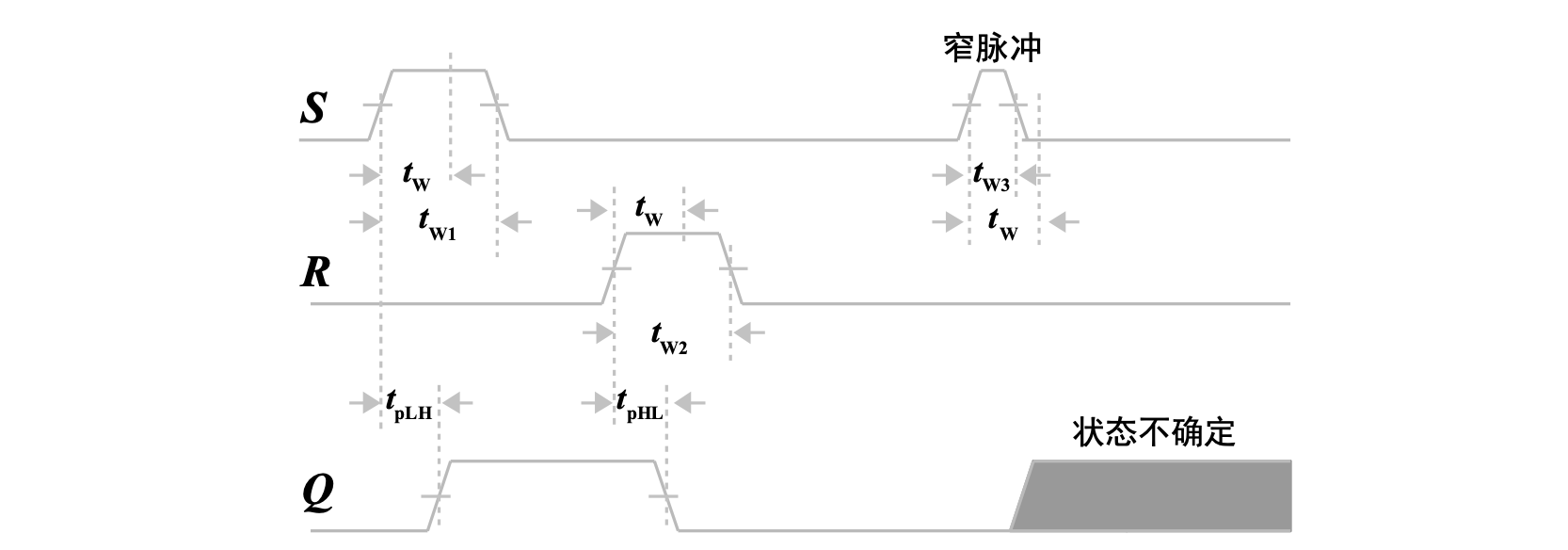

实际的输入输出信号不是瞬间完成变化的,而是存在一段时间来上升和下降。将各输入输出信号的电平以时间轴画出的图叫做「定时图」,描述了各输入信号与输出响应信号之间的时间关系。SR 锁存器的定时器如下图。

当刚开始

输入信号的脉冲宽度必须要达到某一个值

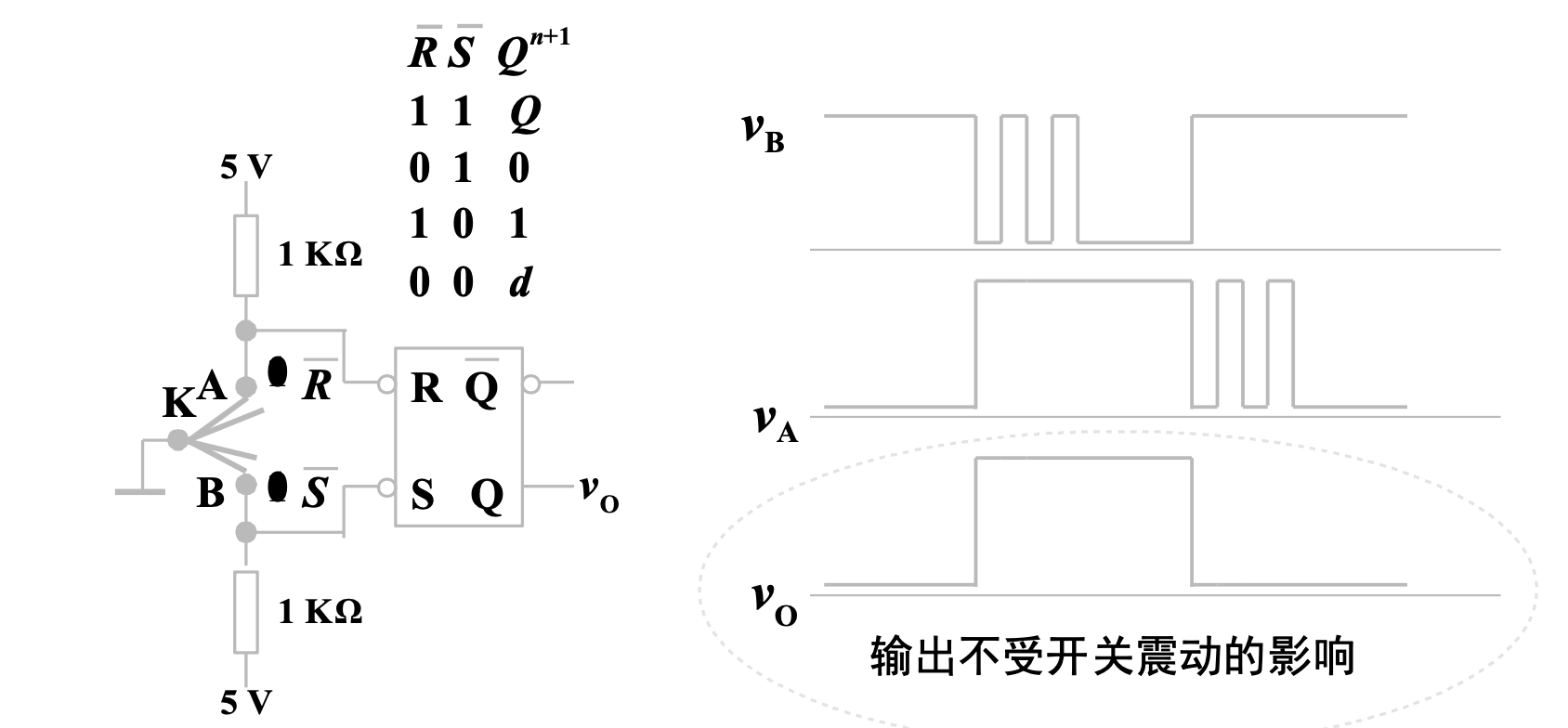

1.4 利用基本 SR 锁存器消去机械开关的振动

机械开关闭合时,

利用 SR 锁存器的性质,设计如下电路

当开关由 A 到 B,

若发生振动,即没有牢牢贴在 B 端,此时两输入端均接高电平,

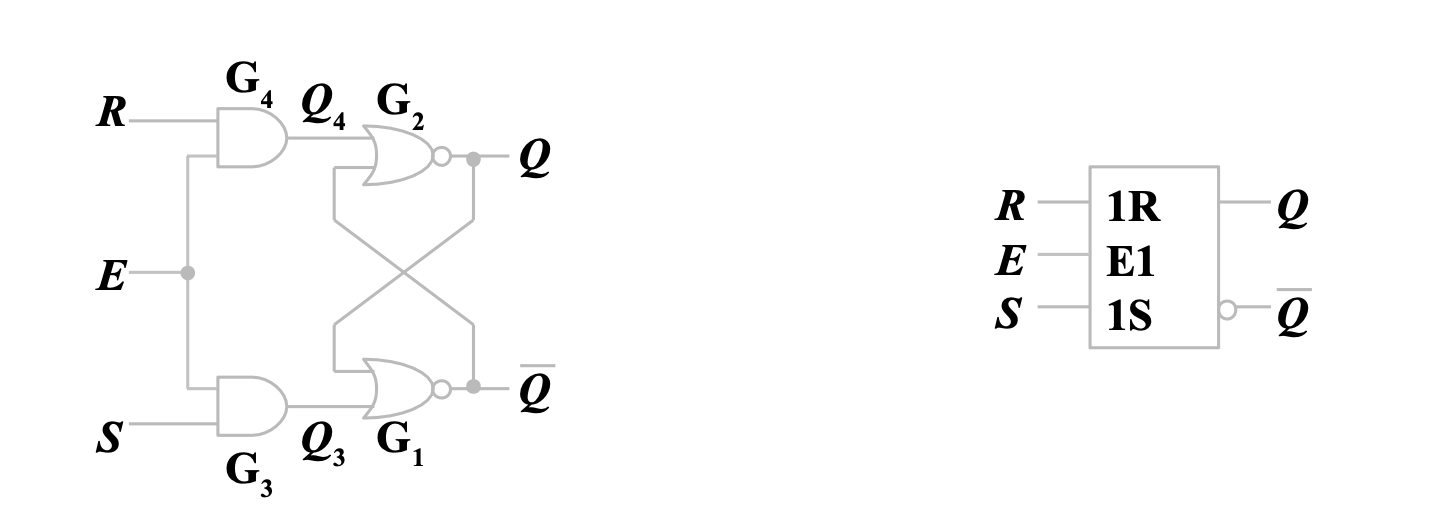

2. 逻辑门控 SR 锁存器

上面的基本

实际应用中,要求锁存器按照一定的时间节拍动作,输入信号收到使能信号

此时使能信号

三、D 锁存器

1. D 锁存器的电路结构

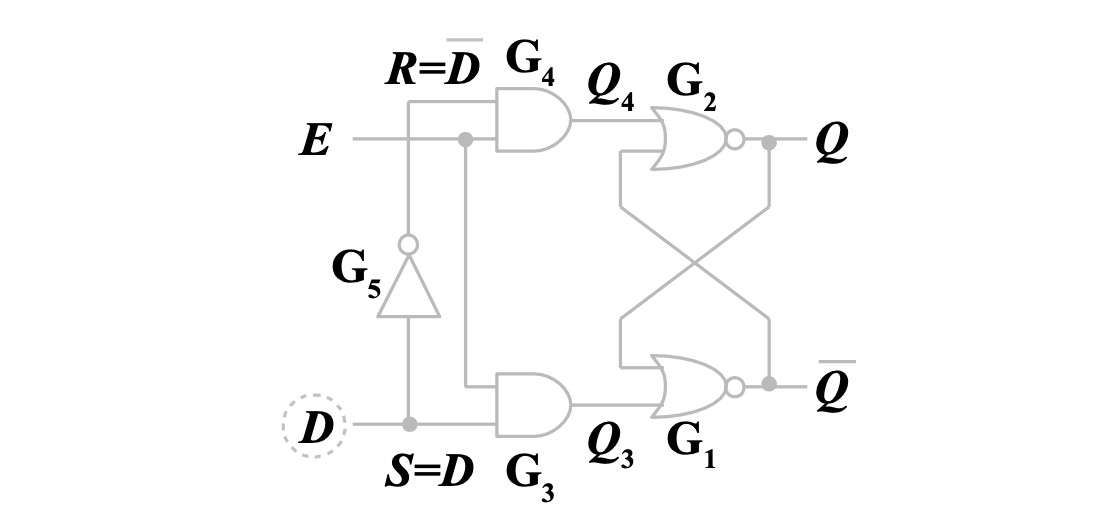

对上一张提到的 SR 锁存器稍作修改,另

由于

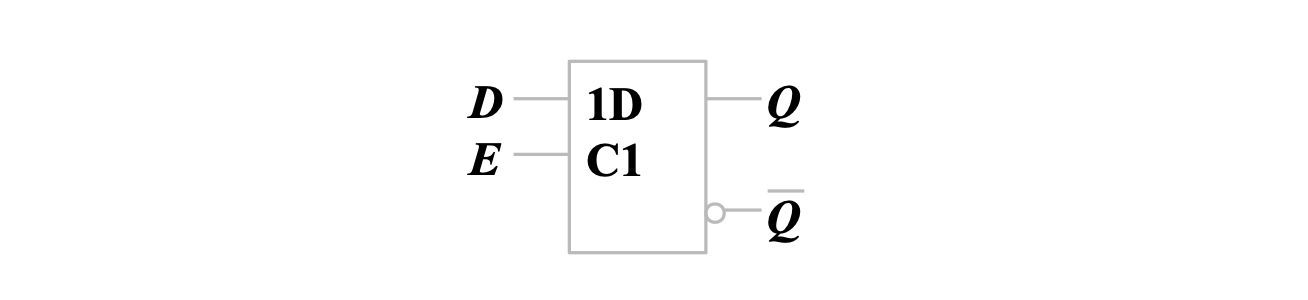

D 锁存器的逻辑符号表示为

其中

| 0 | 0 | Q |

| 0 | 1 | Q |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

2. 典型的 D 锁存器集成电路

74HC/HCT373 八 D 锁存器

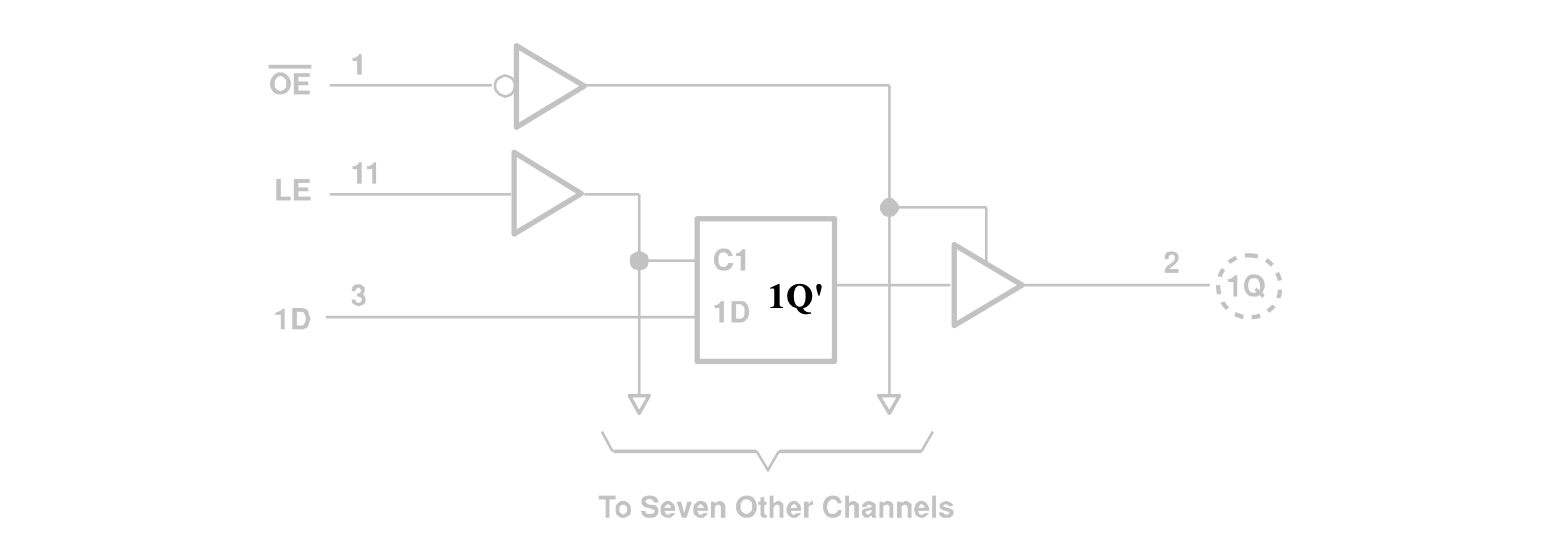

核心电路是 8 个 D 锁存器。74HC373 的内部逻辑图可以表示为

向下的小三角形表示还省略了数个类似的模块。其中

| 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 0 | X | |

| 1 | X | X | Z |

3. D 锁存器的动态特性

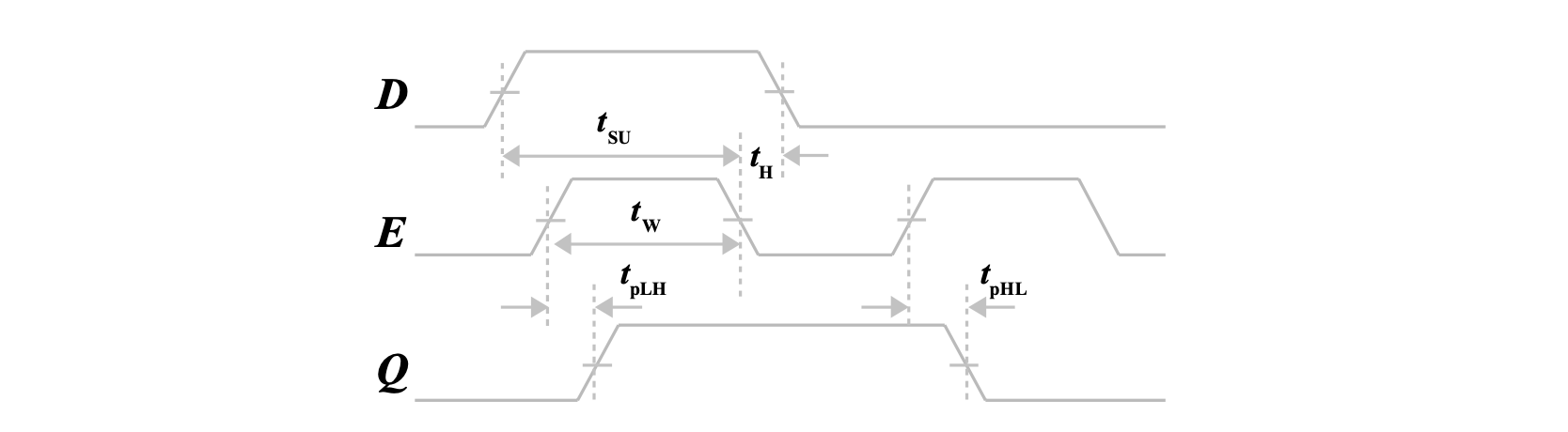

类似于 SR 锁存器,实际的输入输出信号不是瞬间完成变化的,而是存在一段时间来上升和下降。D 锁存器的动态特性图可以表示为

建立时间

保持时间

脉冲宽度

传输延迟时间

若时序不满足要求,在实际电路中的电路状态可能陷入不确定

四、触发器

1. 触发器的电路结构和工作原理

锁存器与触发器

共同点: 具有 0 和 1 的两个稳定状态,一个锁存器或触发器能保存一位码

不同点:

- 锁存器:电平敏感,状态变化由特定电平使能

- 触发器:脉冲沿敏感,状态变化由脉冲有效沿使能

触发器与锁存器不同的是,触发器有一个输入端用于接受时钟信号

触发器有三种典型结构:主从触发器、维持阻塞触发器和利用传输延迟触发器。课内只要求掌握主从结构触发器

2. 主从触发器

2.1 工作原理

基本分析

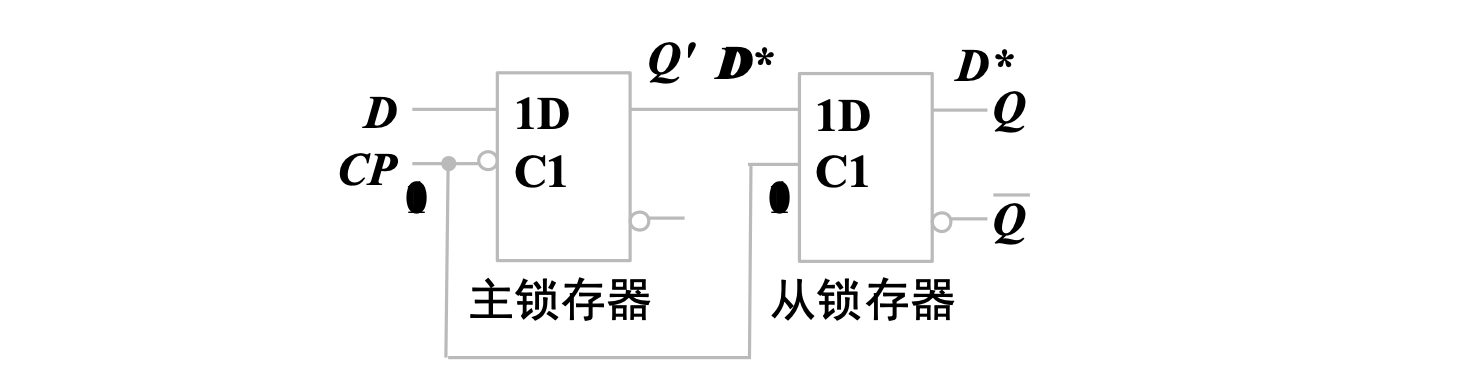

主从触发器由两个锁存器组成,分别称为主锁存器和从锁存器,如下图

主从锁存器有一个输入端

特性方程

D 触发器特性方程可以表示为:

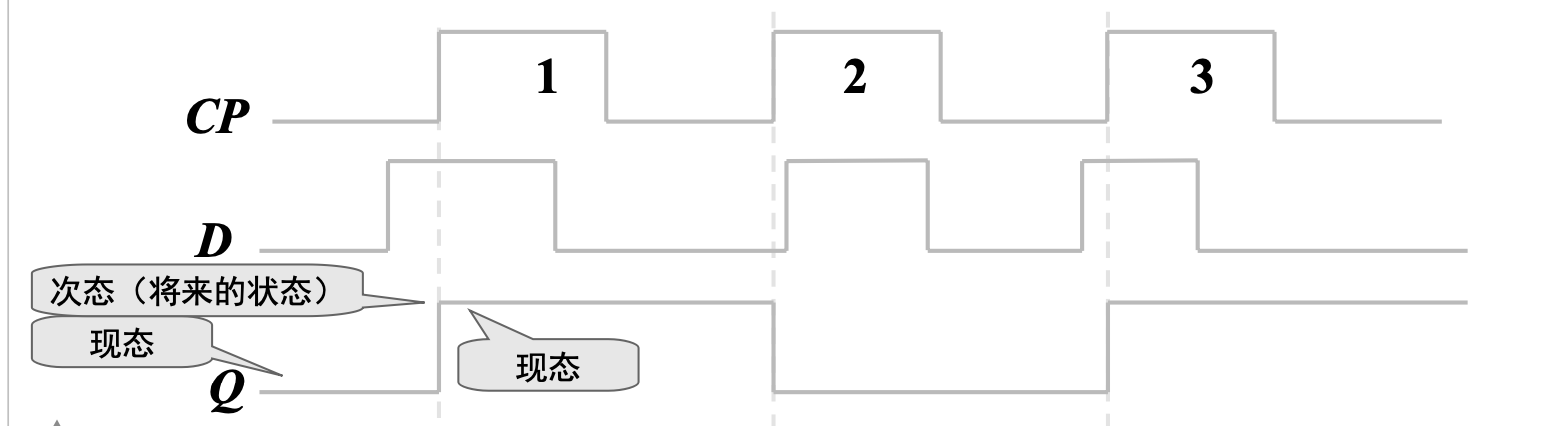

状态变化发生在时钟有效沿到来之后,次态取决于时钟有效沿之前的激励信号

2. 典型集成电路

2.1 异步信号

先介绍一个概念「异步信号」。异步信号表示跟时钟脉冲不同步的信号。在有时钟控制的数字电路中,异步信号独立于时钟脉冲,对电路发挥某种功能。一般情况下,异步信号的优先级大于时钟信号。

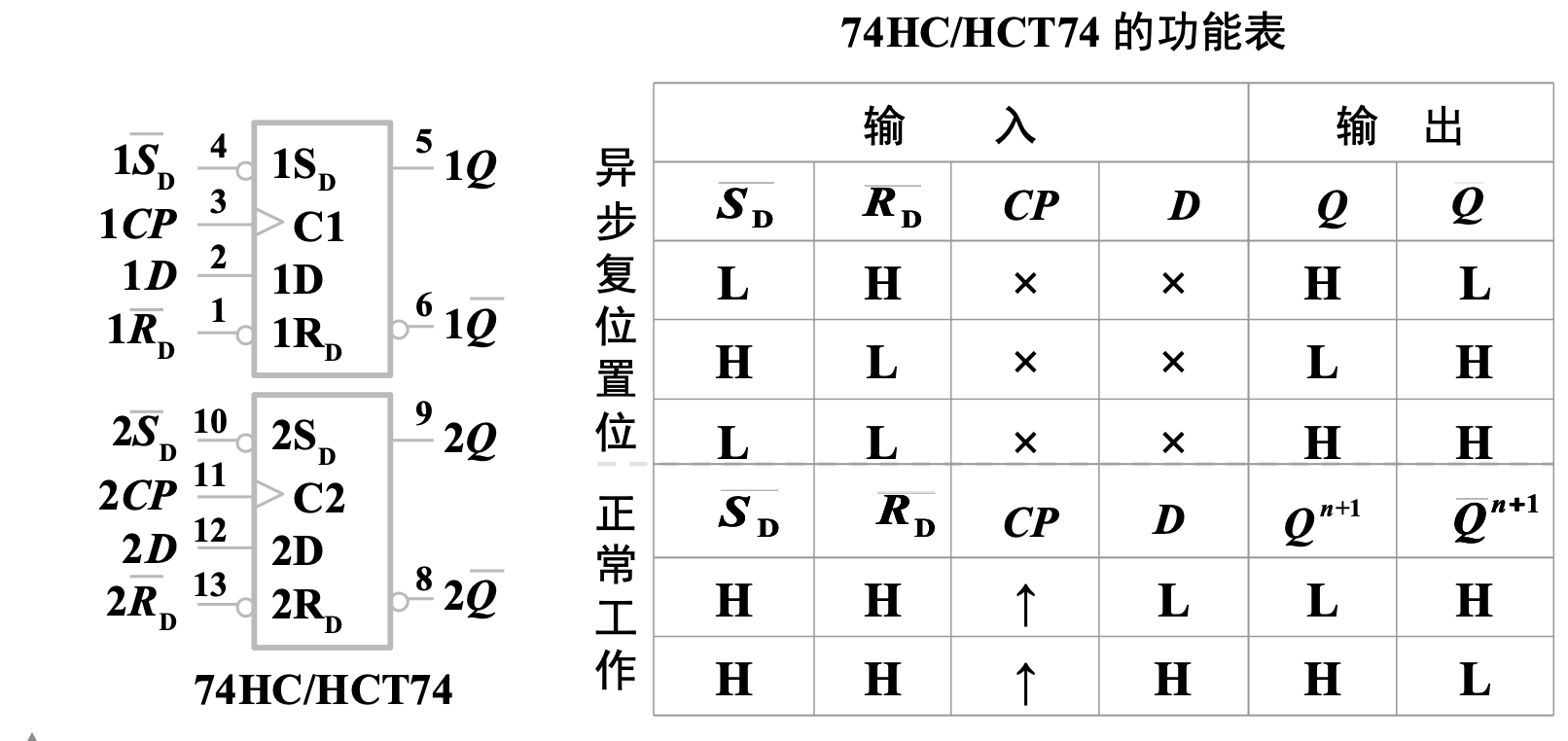

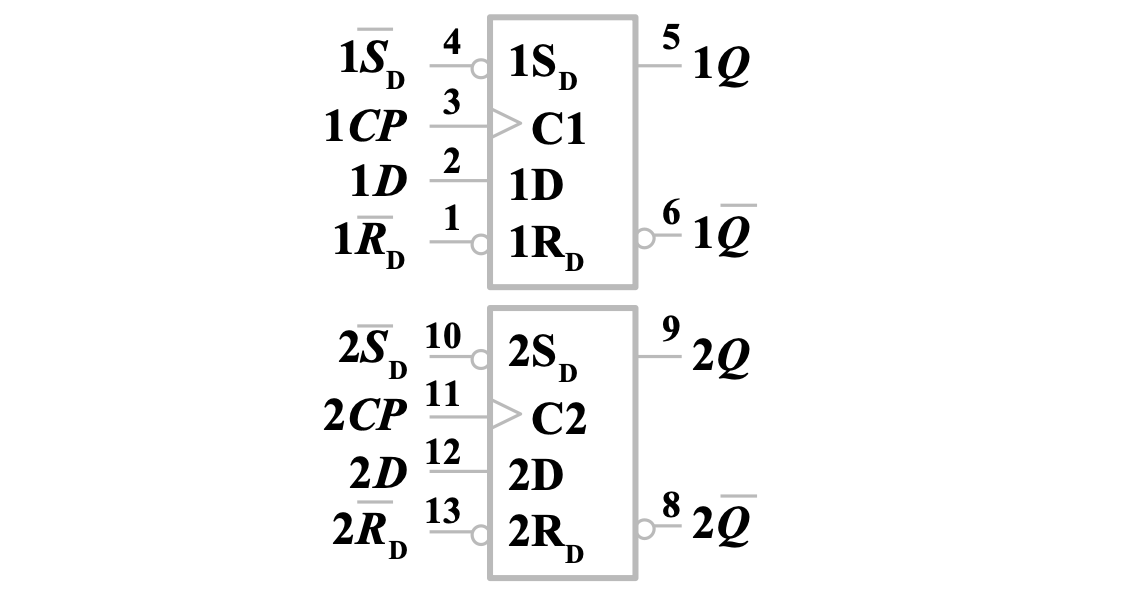

2.2 74HC74

74HC74 为双 D 触发器,包含两个相互的 D 触发器,

, , , ,

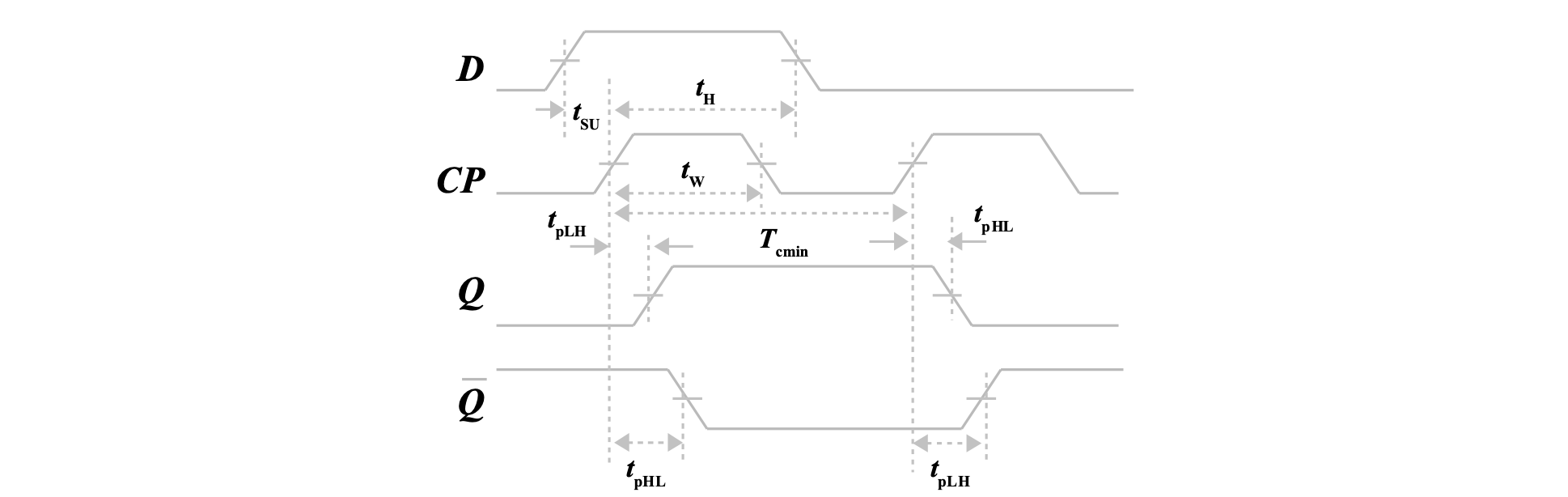

3. 触发器的动态特性

类似于锁存器,实际的输入输出信号不是瞬间完成变化的,而是存在一段时间来上升和下降。D 触发器的动态特性图可以表示为

- 建立时间

- 保持时间

- 脉冲宽度

- 传输延迟时间

- 最高触发频率

五、触发器的逻辑功能

1. 逻辑功能

描述触发器的现态与现态、输入信号之间的逻辑关系叫做「逻辑功能」。触发器的次态不仅与输入信号有关,而且与状态有关。

触发器逻辑功能可以通过表述方式:

- 特性表

- 特性方程

- 状态图

- 波形图

等方式来进行描述

按照触发器逻辑功能,通常分为

2. 常见触发器的逻辑功能

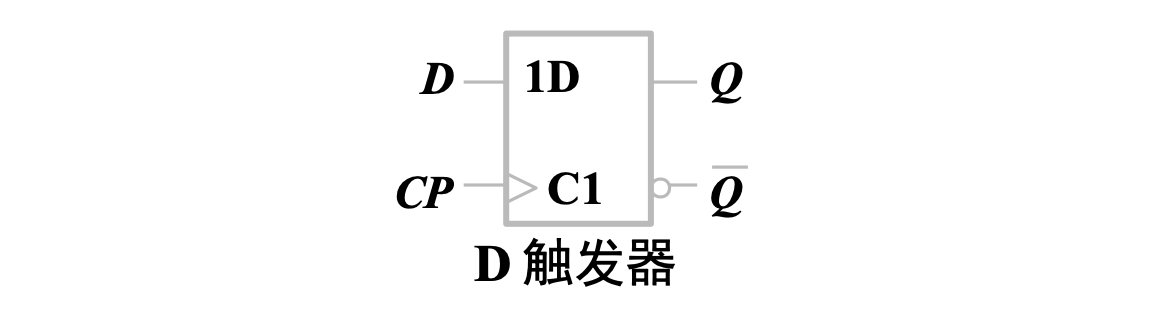

2.1 D 触发器

逻辑符号为

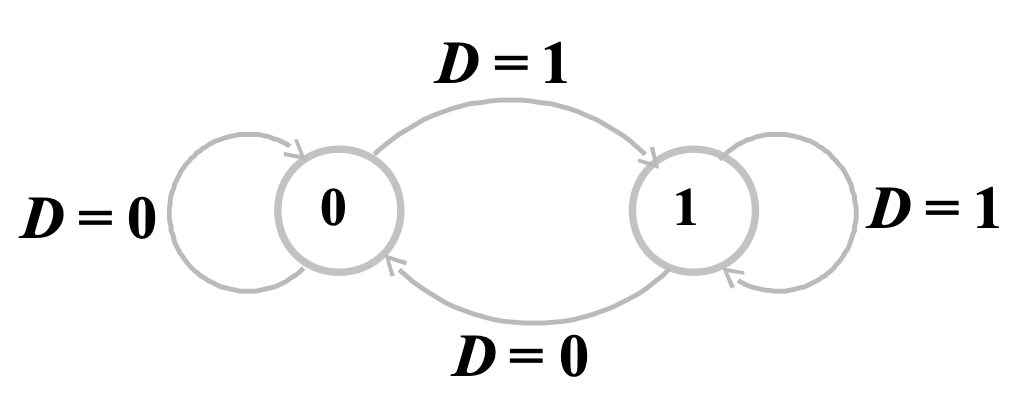

功能表

| 功能 | ||

|---|---|---|

| 0 | 0 | 置0 |

| 1 | 1 | 置1 |

特性表

| Q | D | |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

特性方程

状态图

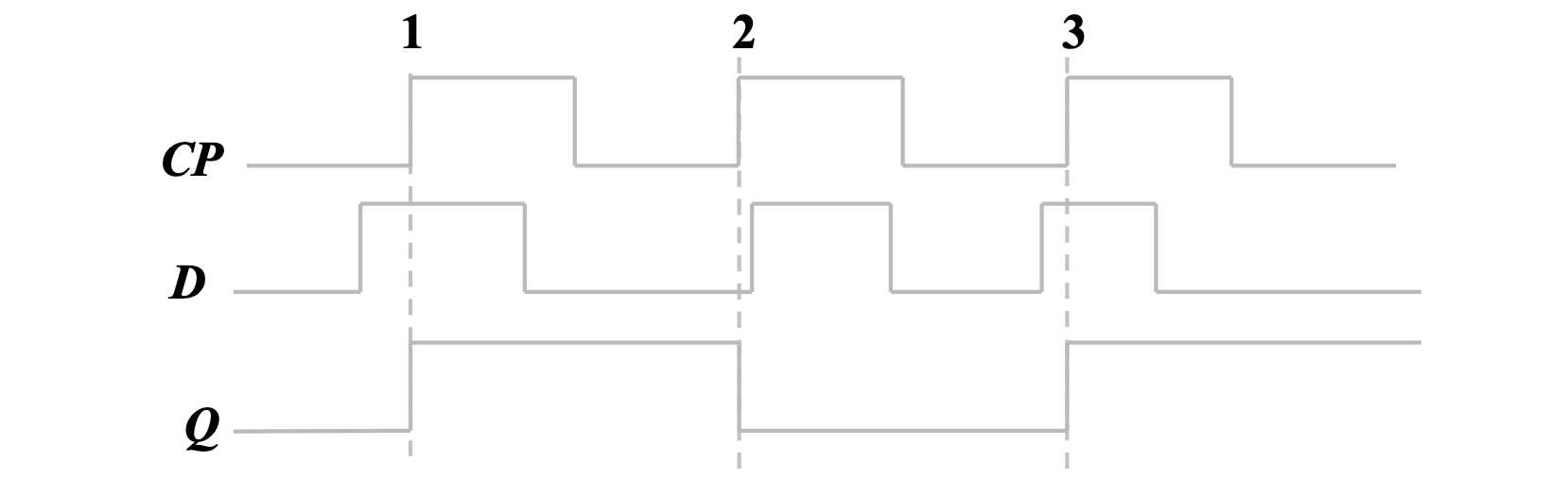

波形图

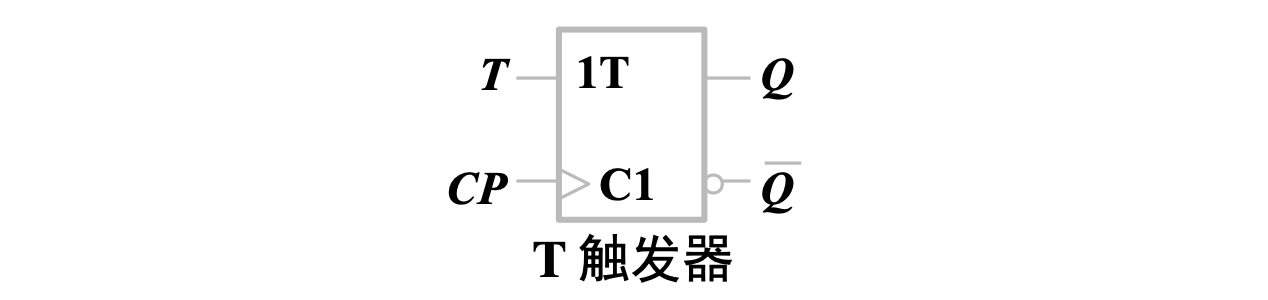

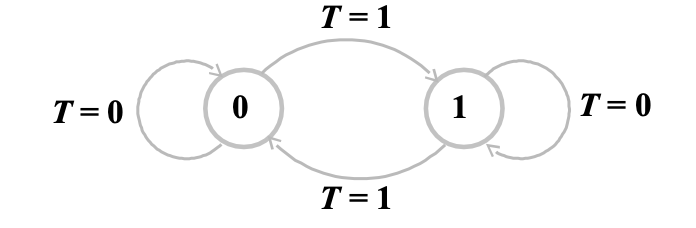

2.2 T 触发器

功能表

| 功能 | ||

|---|---|---|

| 0 | Q | 保持 |

| 1 | 翻转 |

特性表

| Q | T | |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

特性方程

状态图

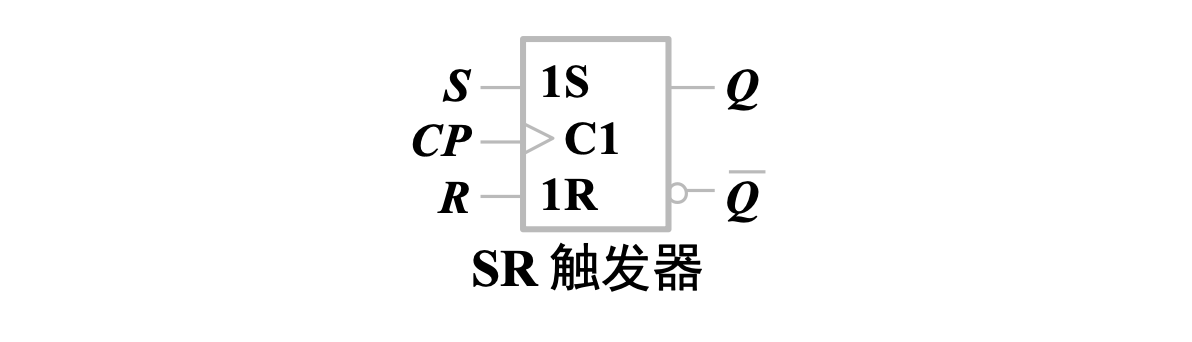

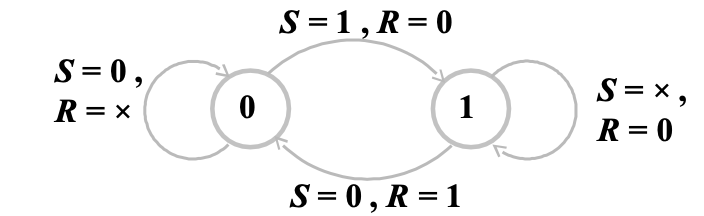

2.3 SR 触发器

不允许

设

功能表

| S | R | 功能 | |

|---|---|---|---|

| 0 | 0 | Q | 保持 |

| 0 | 1 | 0 | 置零 |

| 1 | 0 | 1 | 置1 |

| 1 | 1 | d | 不定 |

特性表

| Q | S | R | |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | d |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | d |

特性方程

其中约束方程为

状态方程

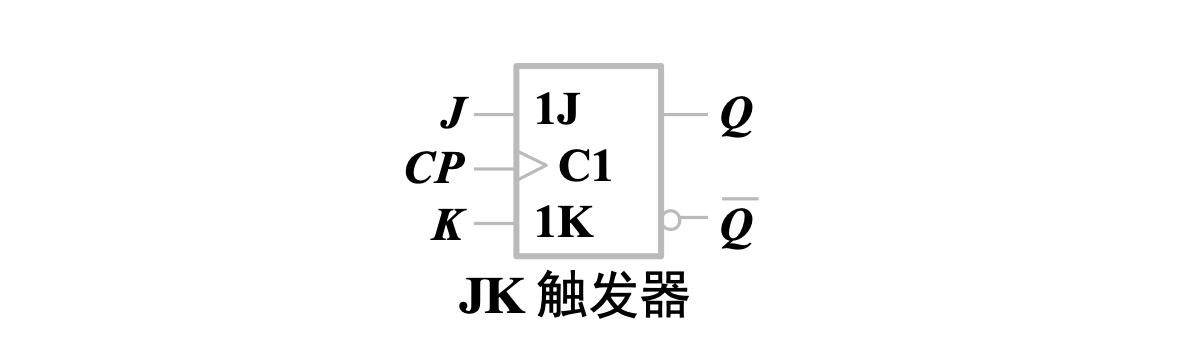

2.4 JK 触发器

J和K同时有效时,状态翻转

设

功能表

| J | K | 功能 | |

|---|---|---|---|

| 0 | 0 | Q | 保持 |

| 0 | 1 | 0 | 置零 |

| 1 | 0 | 1 | 置1 |

| 1 | 1 | 翻转 |

特性表

| Q | J | K | |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | q |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

特性方程

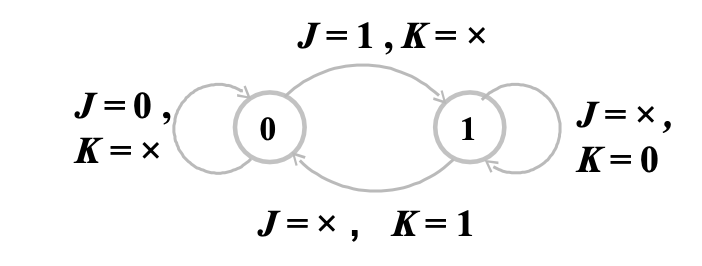

状态图

3. 触发器转换

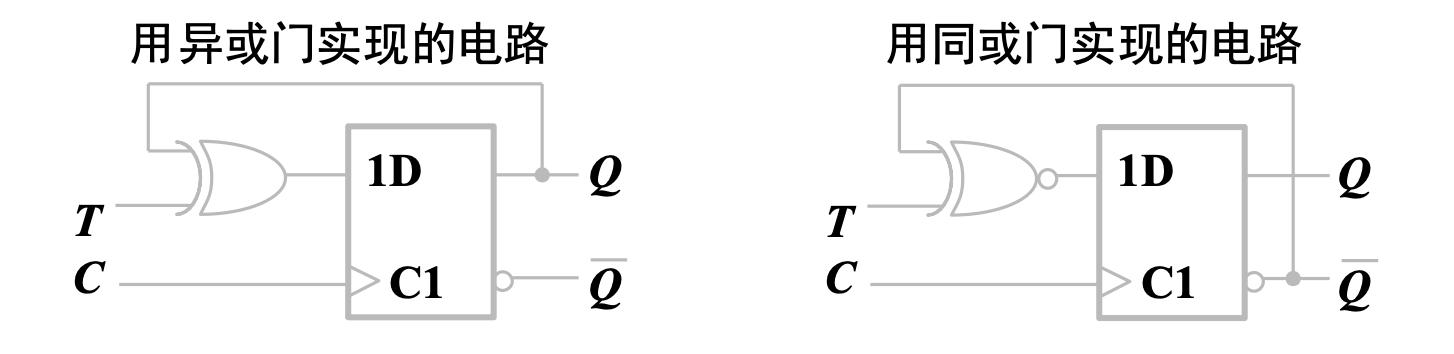

3.1 D 触发器构成 T 触发器

已有 D 触发器(原触发器),实现 T(新触发器)功能

采用特性方程联立法

- D 触发器特性方程

- T 触发器特性方程

比较得

因此可以用同或门或异或门来实现

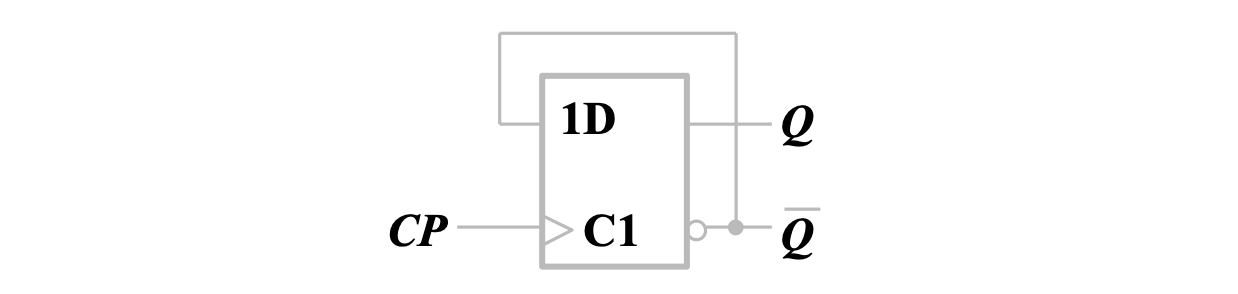

3.2 D 触发器构成 T' 触发器

已有 D 触发器(原触发器),实现 T'(新触发器)功能

采用特性方程联立法

- D 触发器特性方程

- T 触发器特性方程:

比较得

只需要将反相输出端作为输入端即可

六、Verilog 描述锁存器和触发器

1. verilog 行为描述

- initial 过程块:描述仿真初始化的行为,与电路逻辑综合无关

- always 过程块:描述敏感事件发生时,电路一贯的行为过程。

always @(敏感事件表)

begin

定义过程快内的局部变量

过程赋值语句

end

1.1 always 过程块

电平敏感事件

always @(EN,_CR)

EN 或 _CR 电平变化事件发生时,电路一贯的行为过程

边沿敏感条件

always @(posedge CP,negedge _CR)

CP 的上升沿或 _CR 的下降沿到来事件发生时,电路一贯的行为过程

1.2 过程赋值语句

- = 为阻塞赋值,按序赋值

- <= 为非阻塞赋值,无序赋值

有序赋值时,必须按照顺序从上而下赋值,

不同的赋值方式得到不同的电路,如使用阻塞赋值时

always @(posedge clk)

begin

x = d;

y = ~x; // 实际语义为 x = d; y = ~d;

end

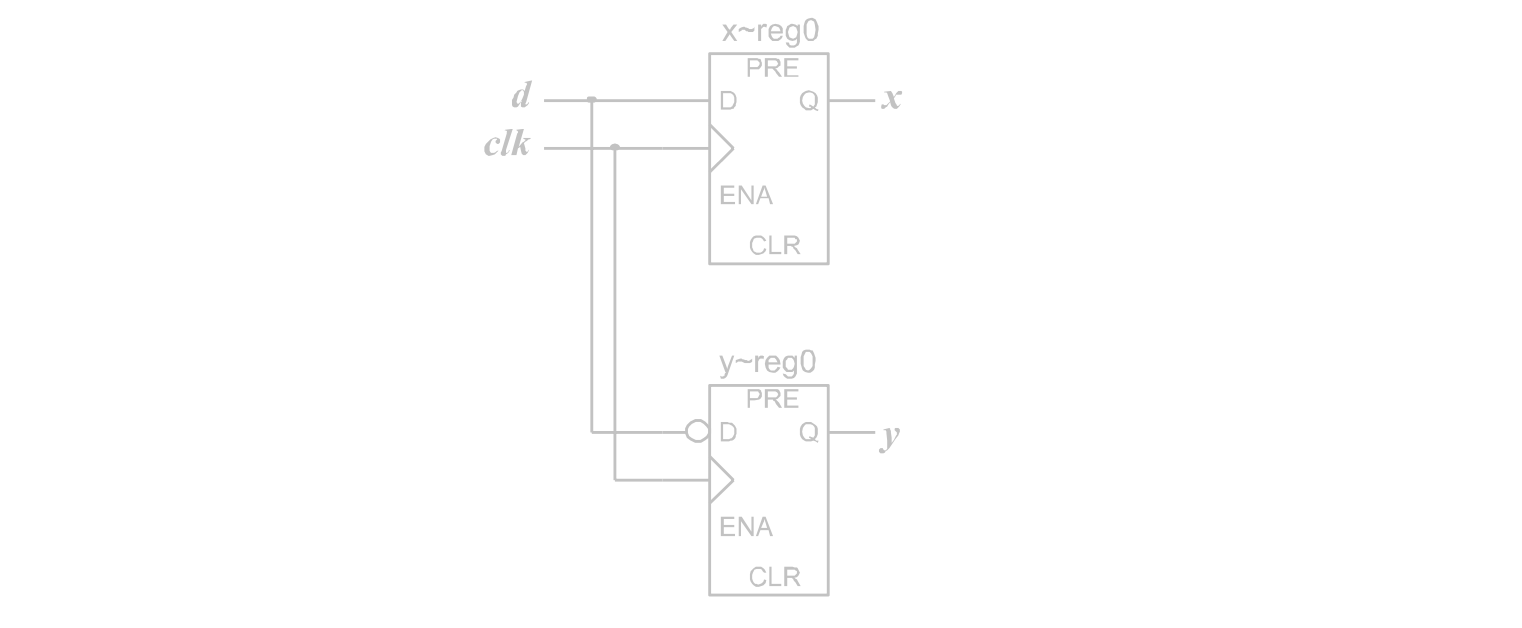

得到的电路为

而若采用非阻塞赋值

always @(posedge clk)

begin

x <= d;

y <= ~x;

end

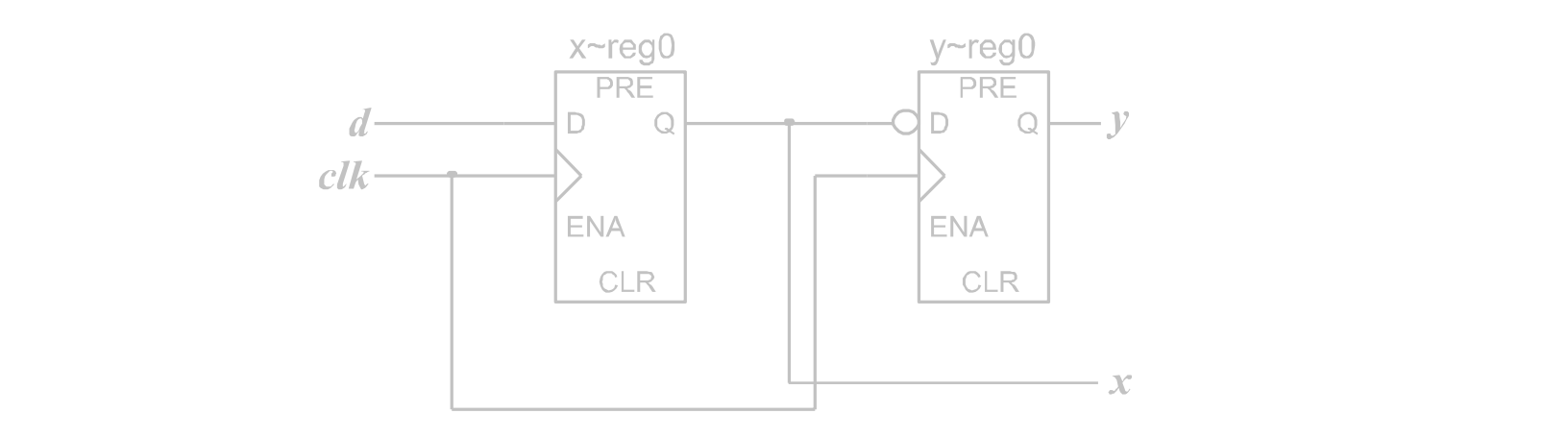

得到的电路为

2. 典型的锁存器和触发器

module D_latch(output reg Q, input D, E); // D 锁存器

always @(E or D)

if (E) Q <= D;

end module

module DFF(output reg Q, input D, CP) // D 触发器

always @(posedge CP);

Q <= D;

endmodule