一、逻辑门电路简介

1. 逻辑门

实现基本逻辑运算和复合逻辑运算的单元电路称为逻辑门,由一个个逻辑门组成的电路称为逻辑电路。

逻辑门电路根据其构造可以分为

- 分立门电路

- 二极管电路

- 三极管电路

- 集成门电路

- MOS 门电路

- TTL 门电路

接下来对其中比较重要的几种做简单介绍

2. TTL 门电路

晶体管-晶体管逻辑电路(Transistor-Transistor Logic),简称为 TTL ,是应用最早,技术比较成熟的集成电路,曾被广泛应用。随着材料和工艺技术的发展,不断推出新型的低功耗和高速 TTL 器件。目前在中、大规模集成电路中还有应用

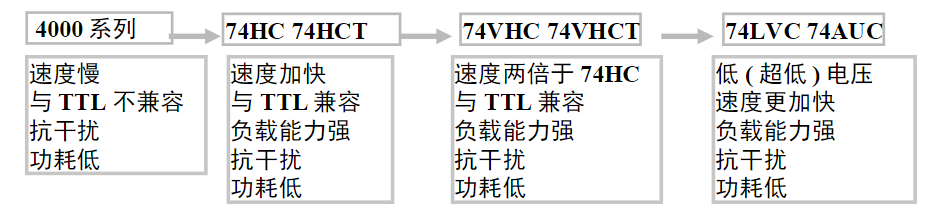

3. CMOS 集成电路

互补金属氧化物半导体(Complementary Metal Oxide Semiconductor)集成电路,简称 CMOS,速度已赶超 TTL 电路,功耗和抗干扰能力远优于 TTL 电路,目前已广泛应用于超大规模、甚大规模集成电路

未用的输入端不允许悬空

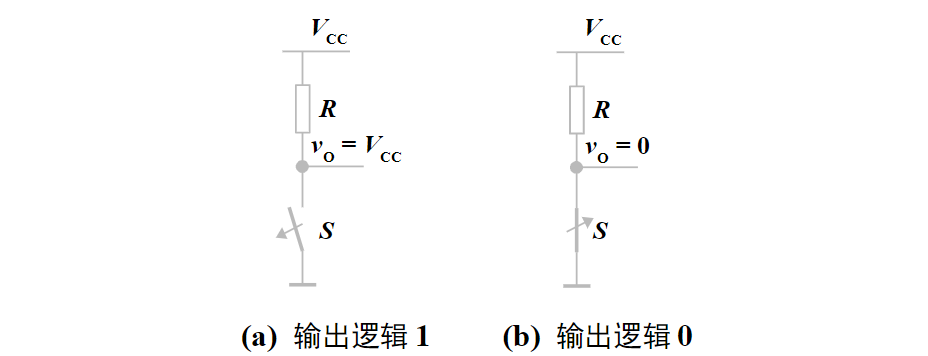

4. 开关电路

逻辑变量取值 0 或 1 ,对应电路中电子器件的“闭合”与“断开”

MOS 管或 BJT 管可作为开关

二、基本 CMOS 逻辑门电路

1. MOS 管及其工作特性

参见模拟电路-MOS

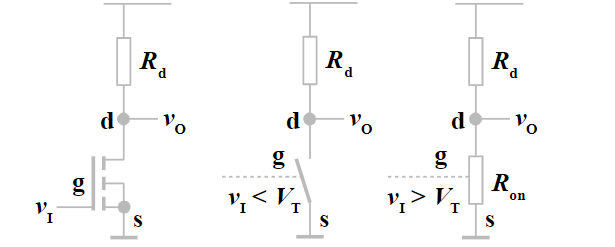

MOS 的开关作用

- 输入低电平时,MOS 管截止,输出高电平

- 输入高电平时,工作在可变电阻区,输出低电平

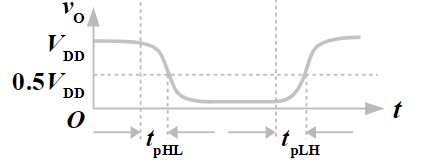

由于 MOS 管栅极、漏极与衬底间电容,栅极与漏极之间的电容存在,状态转换伴随有电容充放电过程

2. MOS 管反相器

2.1 工作原理

通过上文介绍的 MOS 管的开关作用,就可以根据此原理设计 MOS 管反相器,从而构成非门。

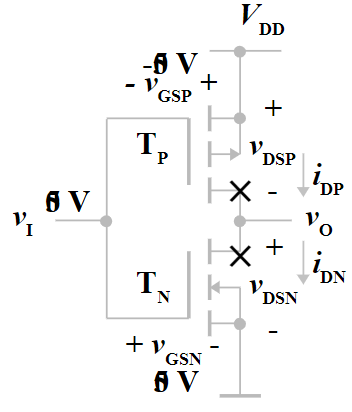

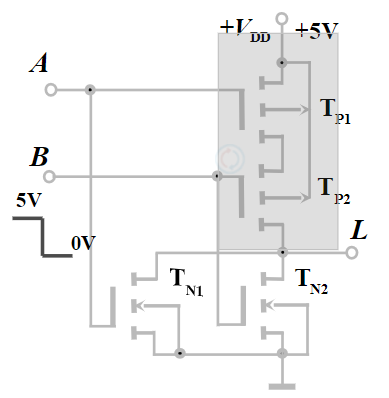

MOS 管反相器由一个 NMOS 和一个 PMOS 并联构成,其电路结构如下图

设

将 PMOS 的源极接在

MOS 管反相器的真值表可以表示为

| 0 | 1 |

| 1 | 0 |

逻辑表达式为

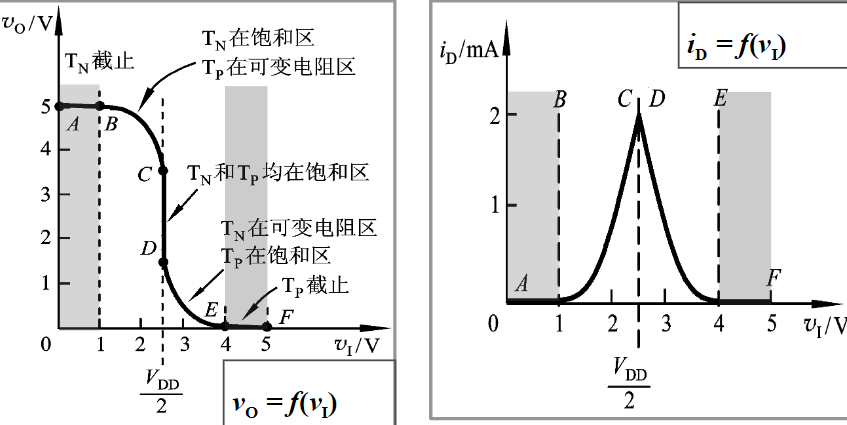

2.2 电压传输特性和电流传输特性

左图为 MOS 反相器的电压特性曲线,右图为电流特性曲线

由

- 当

- 当

因此 MOS 反相器的静态工作功率低

当

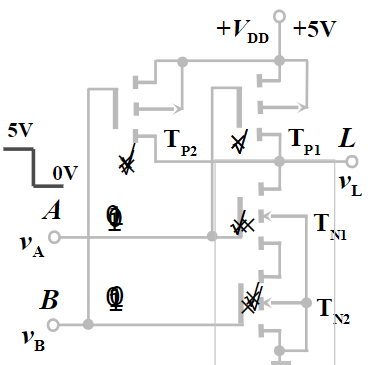

3. CMOS 与非门

类似 MOS 反相器的工作原理,用多个 NMOS 和 PMOS 构成 CMOS 电路,就可以实现各种各样的逻辑门电路。比如最常用的与非门。

其工作原理可以用真值表来表示

| L | ||

|---|---|---|

| 截止 导通 截止 导通 | 1 | |

| 截止 导通 导通 截止 | 1 | |

| 导通 截止 截止 导通 | 1 | |

| 导通 截止 导通 截止 | 0 |

可以表示为

但注意到输入端越多,串联的管子越多,导通时电阻越大,使与非门的低电平升高。因此 CMOS 与非门的输入端不能太多

4. CMOS 或非门

其工作原理可以用真值表来表示

| L | ||

|---|---|---|

| 截止 导通 截止 导通 | 1 | |

| 截止 导通 导通 截止 | 0 | |

| 导通 截止 截止 导通 | 0 | |

| 导通 截止 导通 截止 | 0 |

可以表示为

但注意到输入端越多,串联的管子越多,导通时电阻越大,使与非门的低电平升高。因此 CMOS 与非门的输入端不能太多

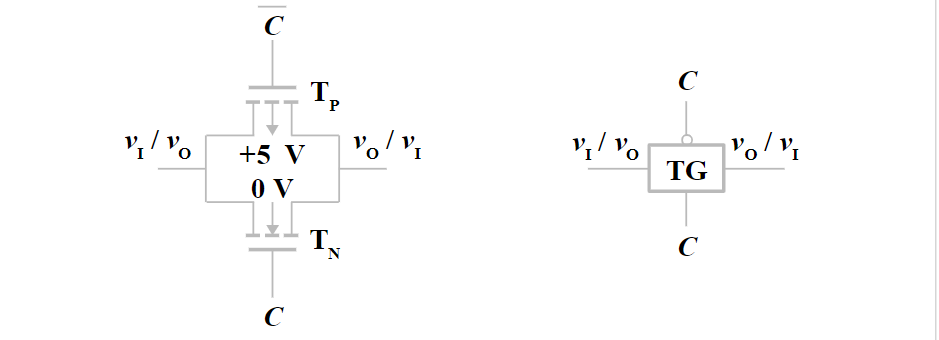

5. CMOS 传输门

传输门的结构及工作原理

在控制信号

设

当

当

此时传输导通,

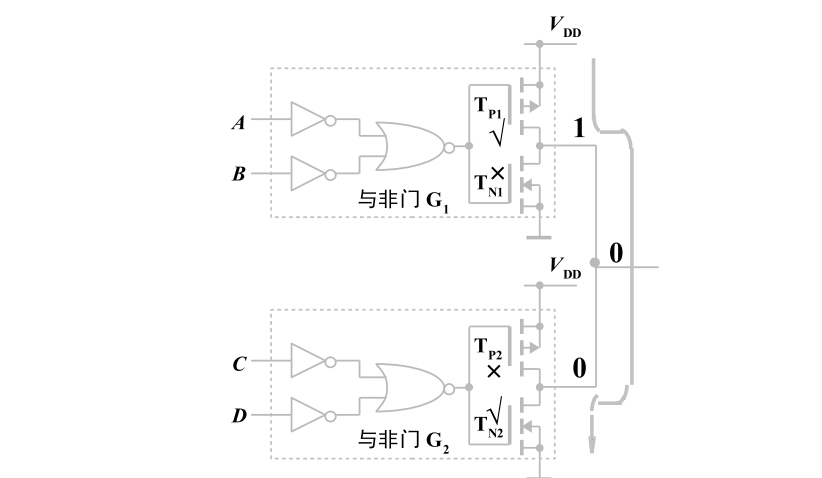

三、CMOS 逻辑门电路的不同结构

1. 缓冲电路

CMOS 门电路在输入,输出端加了反相器作为缓冲电路,缓冲电路能统一参数,使不同内部逻辑集成逻辑门电路具有相同的输入和输出属性,如下图。

2. 输入保护电路和缓冲电路

CMOS 门电路输入端是 MOS 管的栅极,栅极与沟道之间的

设二极管的正向导通电压为

3. CMOS 漏极开路门

普通 CMOS 门电路输出短接,在一定情况下会产生低阻通路,大电流有可能导致器件的损毁,并且无法确定输出是高电平还是低电平。为此,需要在门电路后加上一组 CMOS

- 外接电源和电阻

- 与非逻辑不变

- 可以实现线与功能

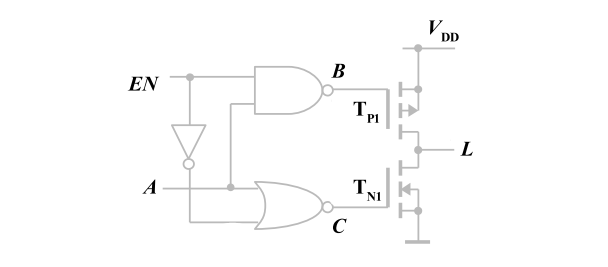

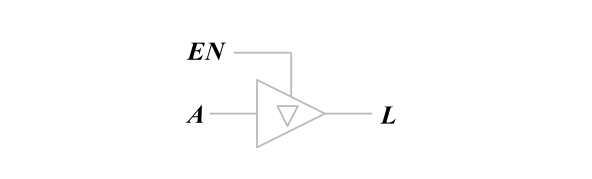

4. 三态 ( TSL ) 输出门电路

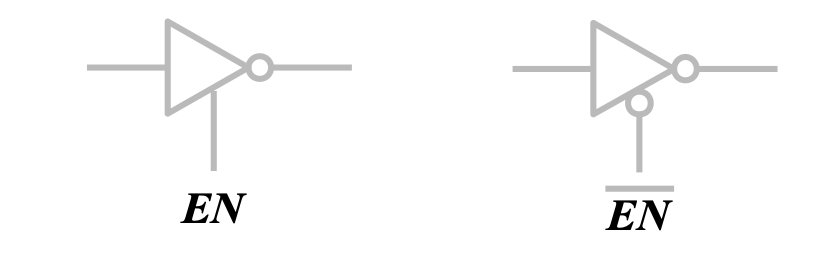

三态门有 3 种输出状态:输出高电平、输出低电平、高阻状态,可以由 CMOS 逻辑门电路构成

逻辑功能为:高电平有效的同相逻辑门,即当使能端

| 使能 |

输入 |

输出 |

|---|---|---|

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| 0 | x | 高阻 |

电路符号为

七、逻辑描述中的几个问题

1. 正负逻辑问题

1.1 正负逻辑的规定

在数字系统中,可用两种逻辑体制表示电路输入和输出的高、低电平

- 正逻辑体制:将高电平用逻辑 1 表示,低电平用逻辑 0 表示

- 负逻辑体制:将高电平用逻辑 0 表示,低电平用逻辑 1 表示

若无特别说明,一般采用正逻辑体制

1.2 正负逻辑等效变换

逻辑内涵一致(电路功能一致)的正、负逻辑表达式是等效的

2. 门电路的等效符号及其应用

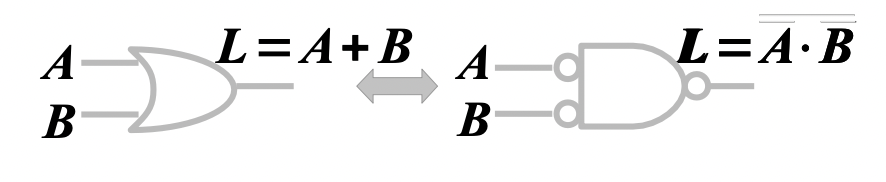

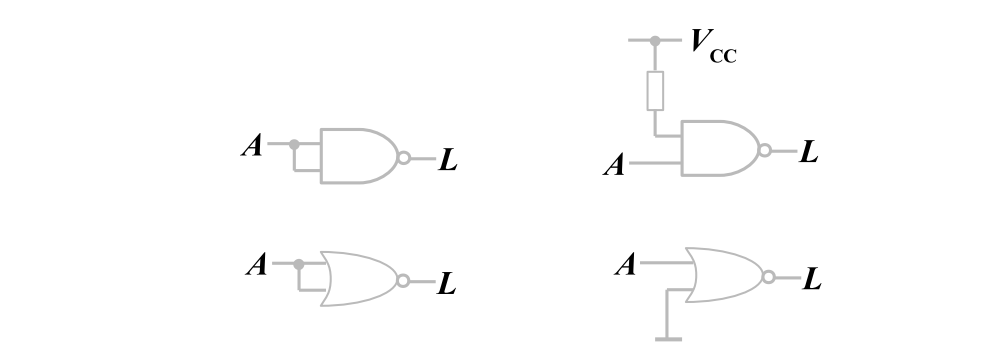

2.1 基本逻辑门电路的等效符号

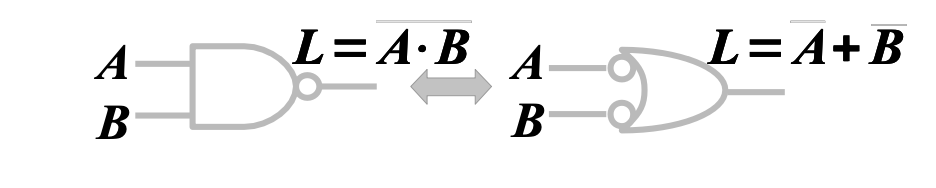

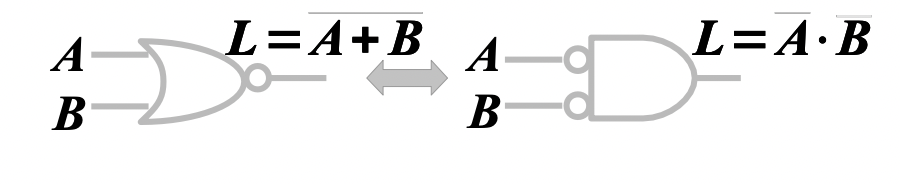

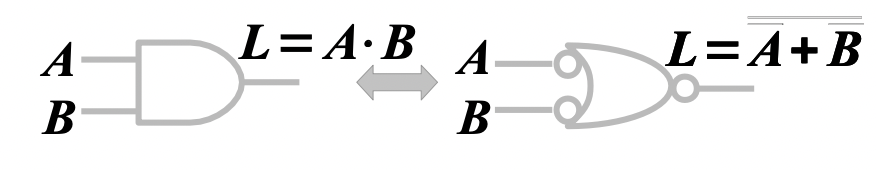

同一逻辑体制下,逻辑内涵一致的逻辑门电路符号,称为等效符号

与非门

或非门

与门

或门

2.2 逻辑门等效符号的应用

利用逻辑门等效符号,可直接变换逻辑电路

2.3 理解高低电平

逻辑门等效符号可强调有效电平,便于理解信号高低电平作用

- 低电平有效:信号低电平时,电路履行预期功能,用反变量形式表示

- 高电平有效:信号高电平时,电路履行预期功能,用原变量形式表示

例如:

- 高电平有效的三态非门,

- 低电平有效的三态非门,

可根据不同控制信号要求,用等效符号描述有效控制信号

八、门电路使用中的几个实际问题

1. 门电路之间的接口问题

各类器件的电压和电流参数各不相同,不同器件连接时,需考虑接口兼容问题

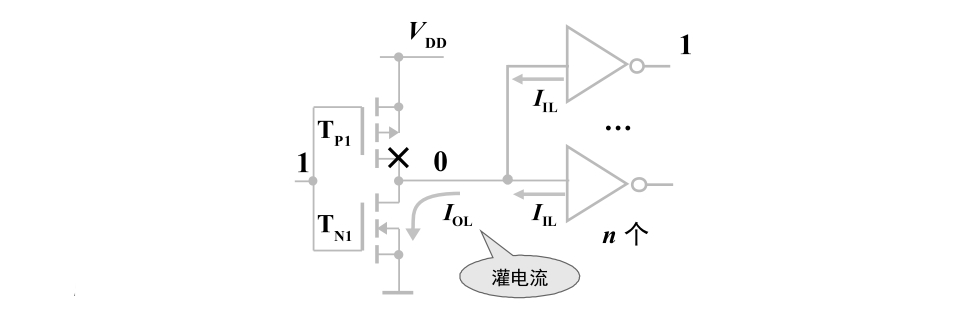

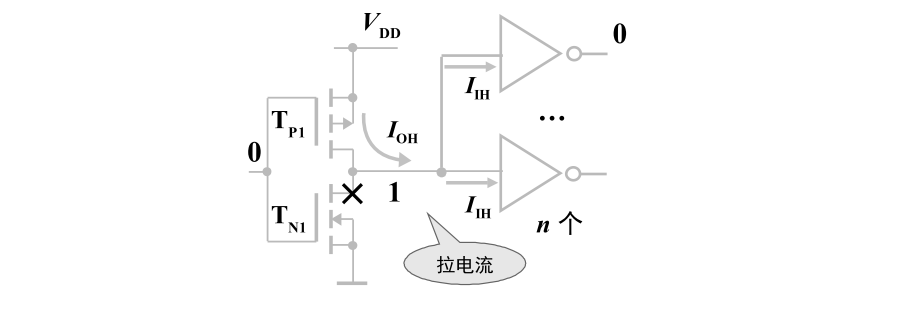

1.1 逻辑电路的扇出问题

驱动器件须对负载器件提供足够大的灌电流或拉电流

灌电流

灌电流情况应满足

拉电流

拉电流情况应满足

1.2 逻辑电平兼容性问题

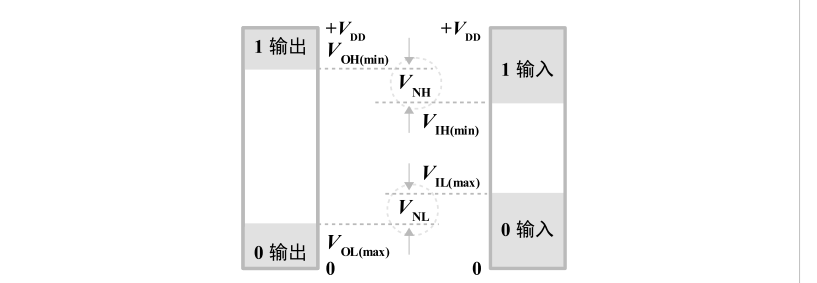

驱动器件输出电压必须处在负载 器件所要求的输入电压范围,包括高、低电压值

驱动门输出高电平应满足

驱动门输出低电平应满足

用图像可以表示为

定义噪声容限为驱动的输出电压和负载的输入电压之差

2. 带负载时的接口电路

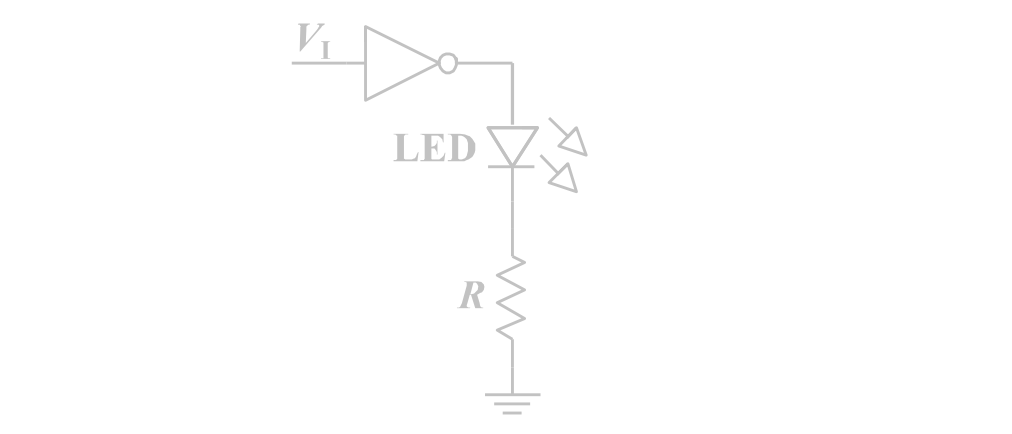

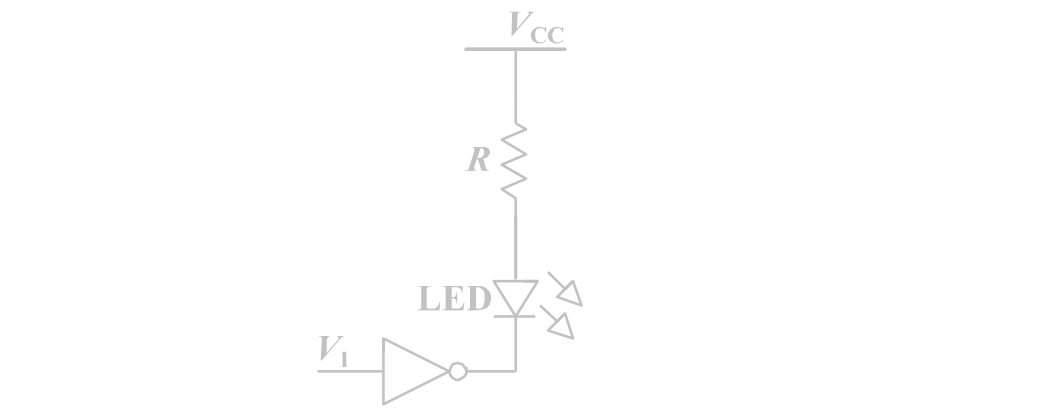

2.1 用门器件直接驱动显示器件

需要加上限流电阻,防止器件电流过大。

用反相器驱动一发光二极管,设 LED 的电流为

门电路输出高电平

限流电阻应满足

门电路输出低电平

限流电阻应满足

3. 抗干扰措施

3.1 多余输入端的处理

处理原则:保证输出逻辑关系正确,避免多余输入端悬空以防干扰

可以将多余输入端与其他有效输入端相连,也可以根据与或关系,与门的多余输入端接高电平;或门的多于输入端接低电平

要考虑驱动门的扇出数

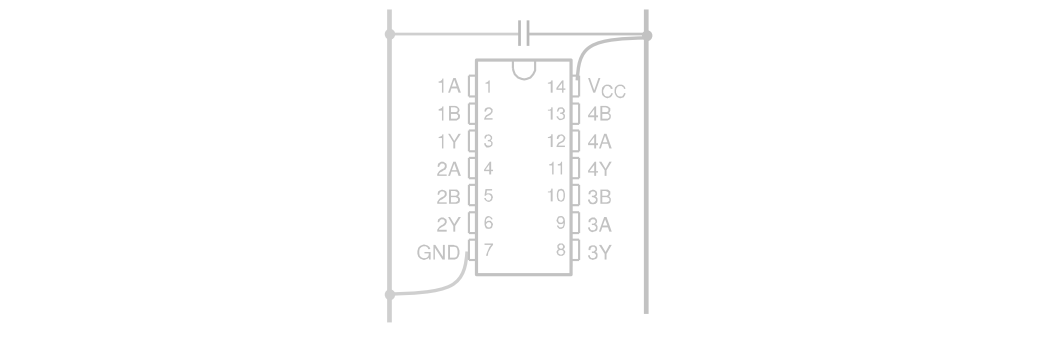

3.2 去耦合滤波电容

一般电源是非理想的,存在一定内阻,数字电路在高、低状态之间交替变化时,可能会与电源产生相互影响,造成逻辑功能错乱,常采用去耦合滤波电容:

- 在本电路板电源与地之间加一个10~100uF 的大电容器

- 各芯片的电源引脚附近(越近越好)与地之间加一个 0.1uF 的电容器