一、只读存储器

1. 概述

半导体存储器时数字系统不可缺少的组成部分,用来存放大量二值数据,通常使用在大规模集成电路中

存储器可以分为

- RAM(Random-Access Memory)

- SRAM,即静态 RAM(Static RAM)

- DRAM,即动态 RAM(Dynamic RAM)

- ROM(Read-Only Memory)

- 固定 ROM

- 可编程 ROM

- PROM

- EPROM

- E

- FLASH

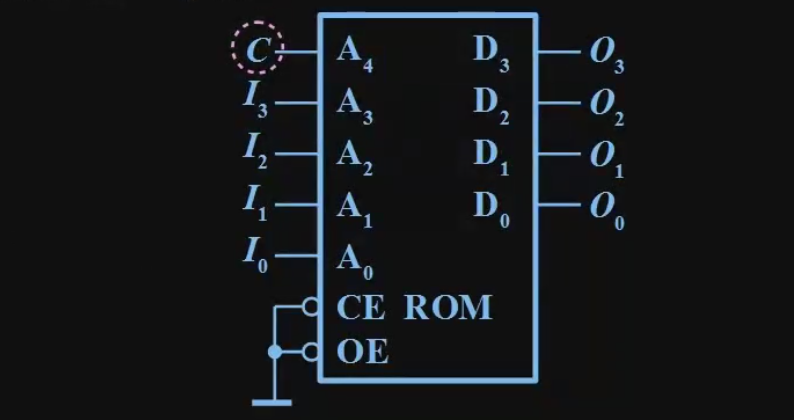

2. ROM 的基本结构

存储器构成

存储器由存储阵列,地址译码器、输出控制电路三部分组成

- 存储阵列:多位存储单元排列成矩阵

- 字:按位编组,每次可以读出一组

- 字长:字的位数

- 地址:每个字的编号

地址译码器能将输入的地址码译成相应的字单元控制信号,从存储矩阵中选出指定的存储单元组(字),并将它送到输出控制电路

基本概念

- 字数:字的总量

- 存储容量(M):存储二值信息总量

字 数 位 数

- 存储单元(Cell):字线与位线的焦点

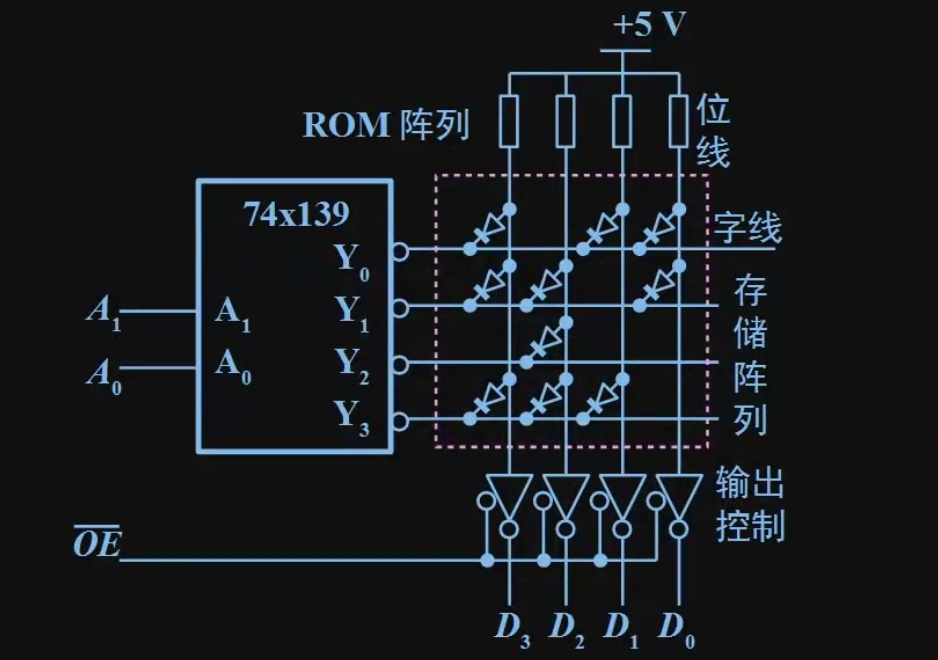

阵列结构

出厂时二极管已经设计好,因此无法对信息进行改写。

字线和位线的交点就是一个存储单元,有二极管的位输出1,没有的输出0

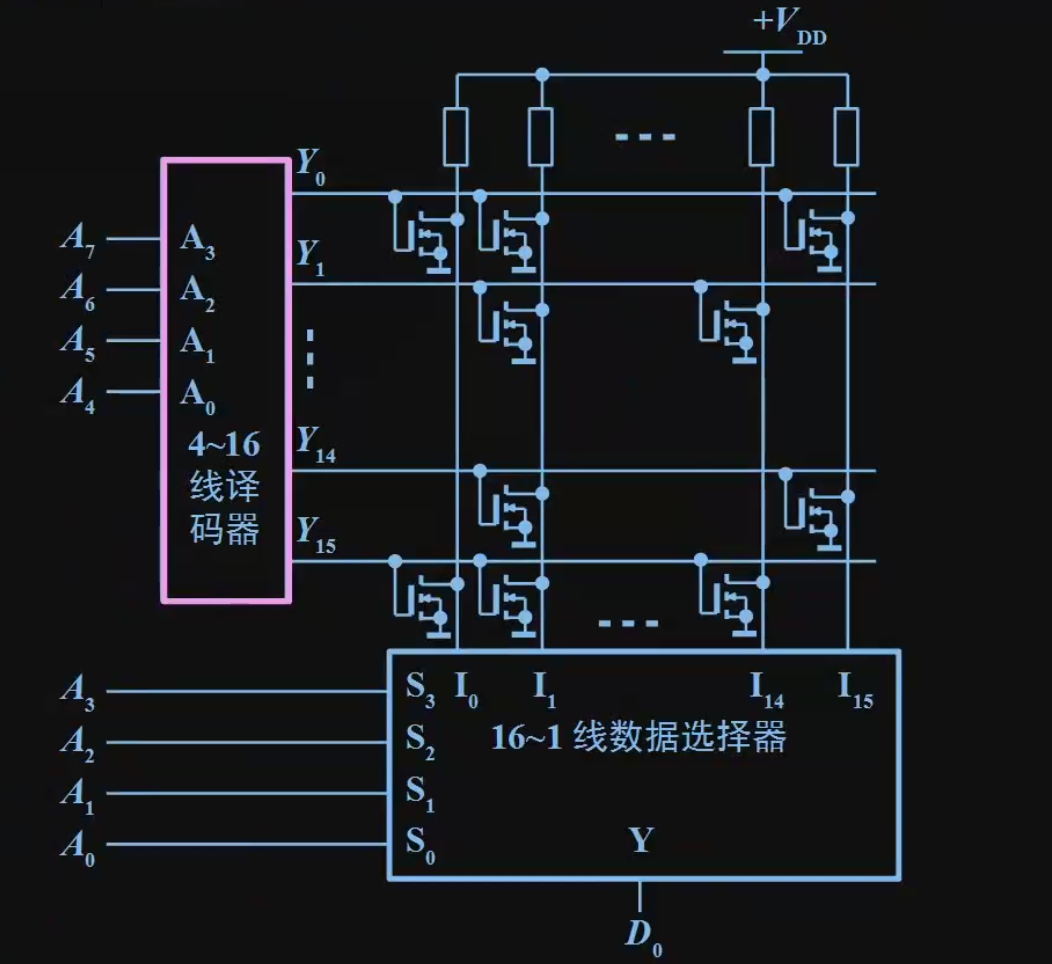

3. 二维译码与存储阵列

有时只需要每个字长为1bit,此时如果用一维译码,会让译码器变得非常复杂。构成

译码器分为左侧的行译码器和下方的列译码器。先从

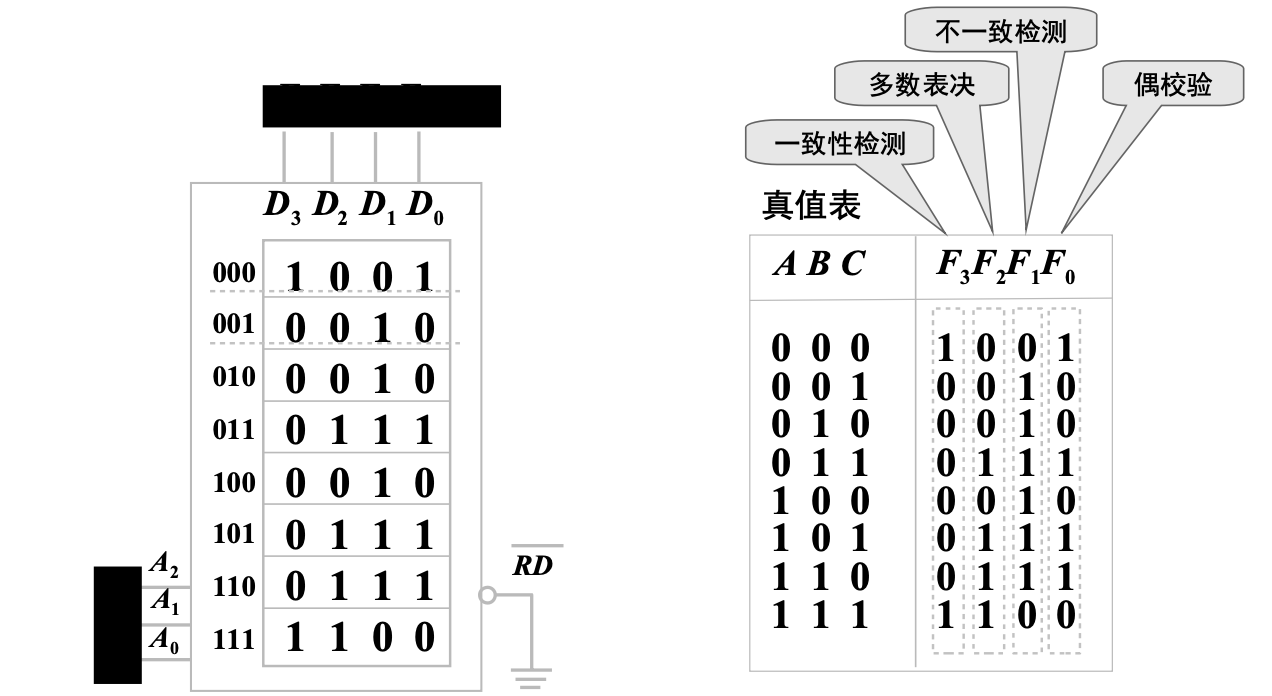

4. ROM 的应用

4.1 组合逻辑电路

ROM 可以实现组合逻辑电路功能。将地址端的输入当成三个变量

4.2 格雷码转换

二、随机读取存储器

RAM 和 ROM 的最大区别是随机读写和掉电即失

RAM 又分为静态 SRAM 和动态 DRAM

1. 静态随机存取存储器

1.1 SRAM 基本结构和输入输出

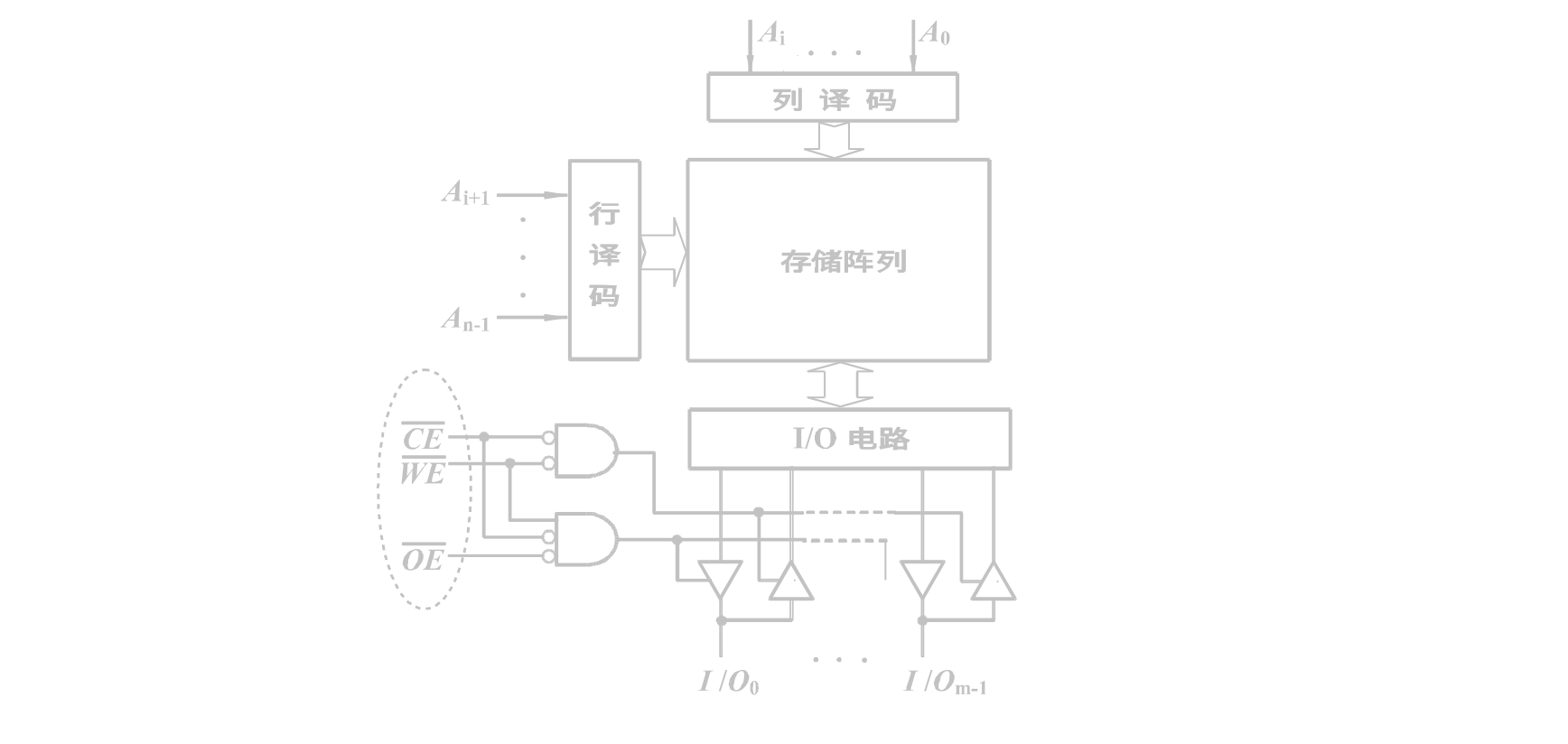

SRAM 由存储阵列、地址译码、I/O 控制三部分组成

工作模式为

| 工作模式 | ||||

|---|---|---|---|---|

| 保持 | 1 | x | x | 高阻 |

| 读 | 0 | 1 | 0 | 数据输出 |

| 写 | 0 | 0 | x | 数据输入 |

| 输出无效 | 0 | 1 | 1 | 高阻 |

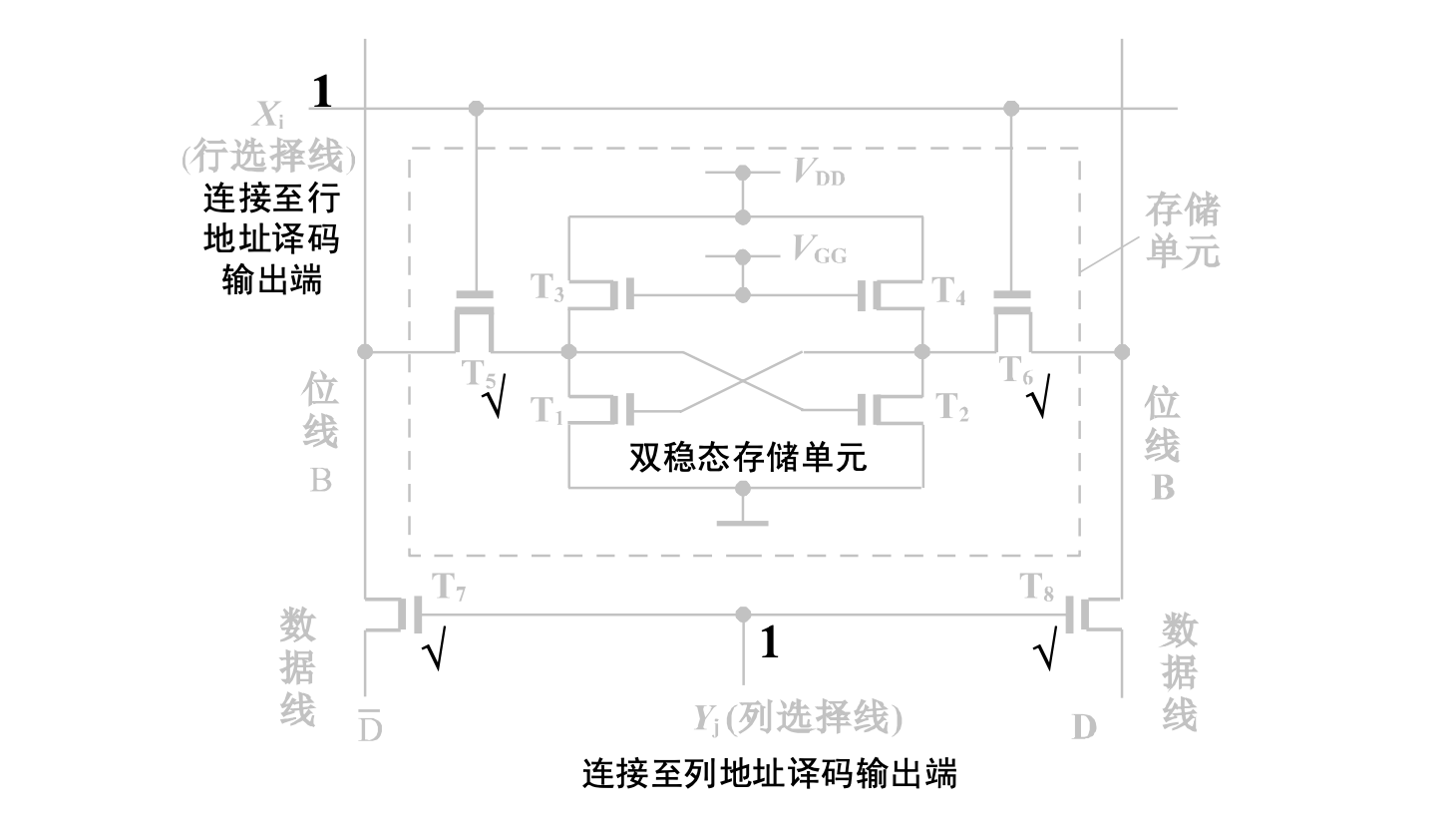

1.2 RAM 存储单元

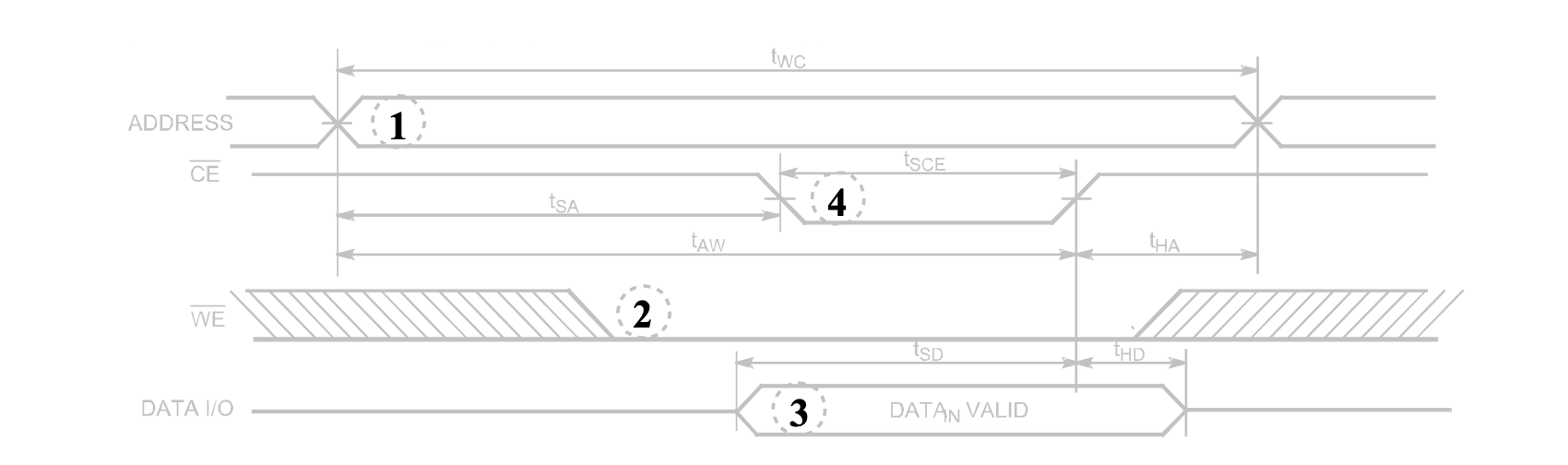

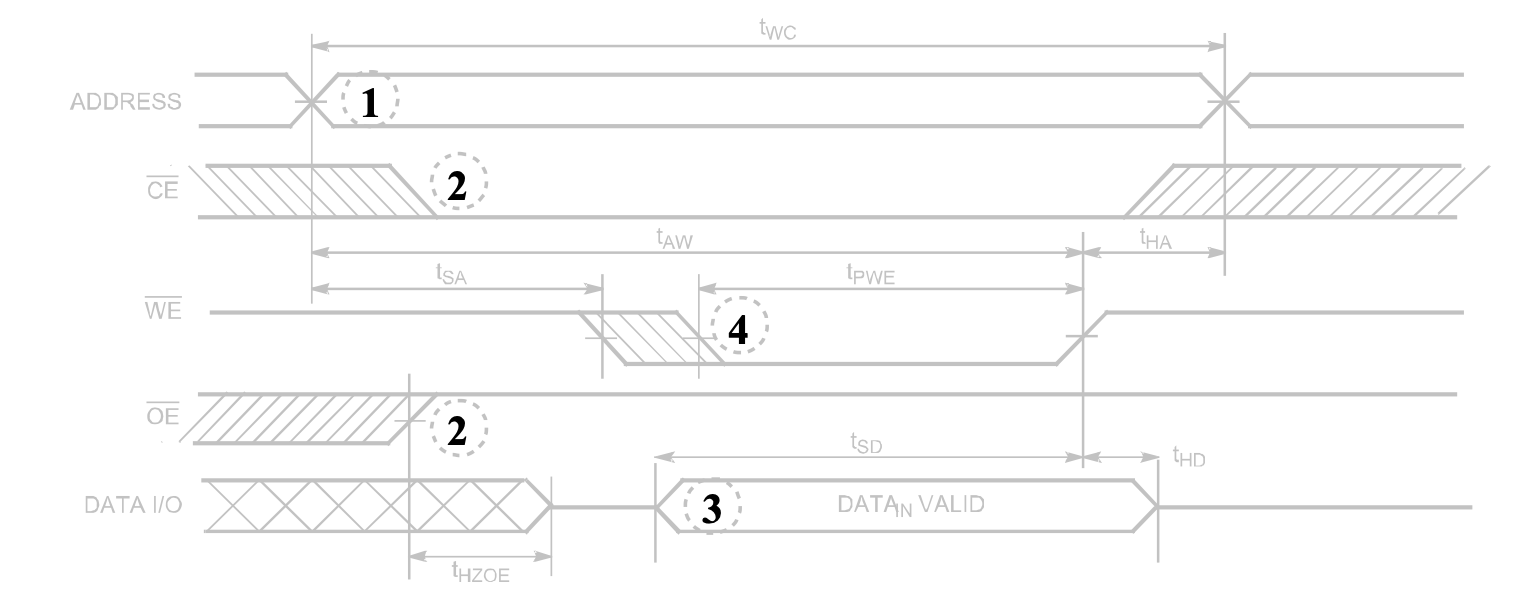

1.3 SRAM 的读写操作及时序图

地址信号控制读时序,前提是

2. 同步静态随机存储器

SSRAM

- SSRAM 的读写操作是在时钟脉冲同步控制下进行的

- SSRAM 增加了地址和输入寄存器、读写和从发控制逻辑电路

- SSRAM 的从发功能:

- 锁存首地址后,在同步时钟作用下,由内部计数器产生连续的偏移地址

- 在连续读写多字时,可减少外部地址总线占用时间,提高读写效率

- 比如:内部的 2 位二进制计数器可产生连续 4 个低 2 位的偏移地址

3. 动态随机存储器

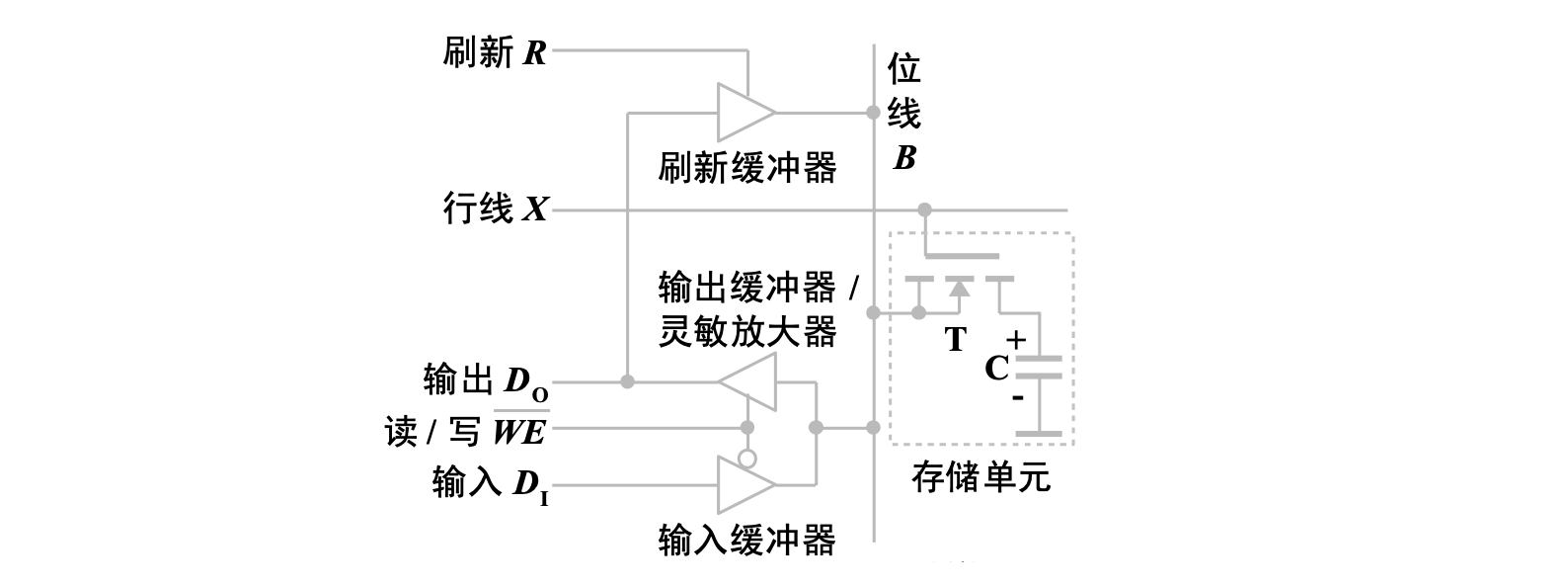

3.1 DRAM

- 静态随机存取存储器 SRAM 存储单元需 6 个 MOS 管,集成度受到限制

- 动态随机存取存储器 DRAM 存储单元需 1 个 MOS 管和 1 个小容量电容

用电容来存储数据,电容充满电表示 1,放完电表示 0。读几次以后,电容会放电,因此需要有刷新回路来重新充电,把输出端的电压引回去。

写操作时,

读操作时,

由于读操作会消耗 C 中电荷,每次读后需要刷新。刷新操作可只选通行线实现。例如当 $X = 1 ,WE=1, R = 1 $,进行刷新,这种刷新是整行刷新

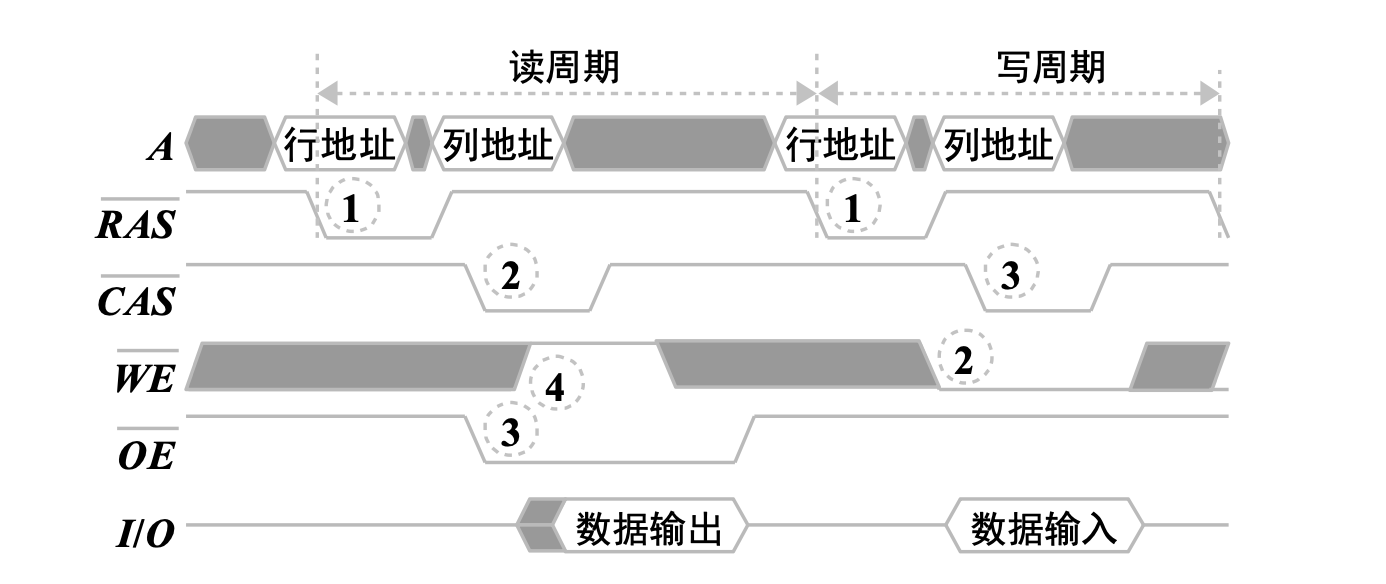

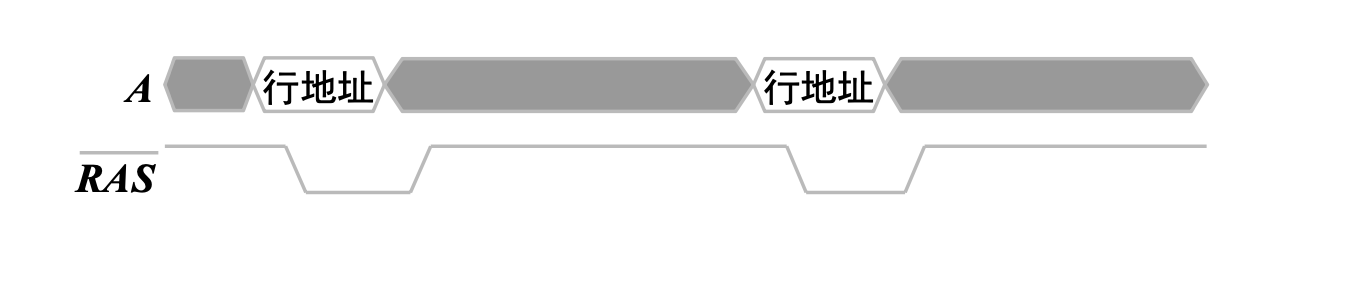

DRAM 集成度高,容量大,为减少地址位,用行、列地址分时共享

3.2 DRAM 操作模式

读写操作:行列地址分别送入地址寄存器后,在使能信号控制下完成读写操作

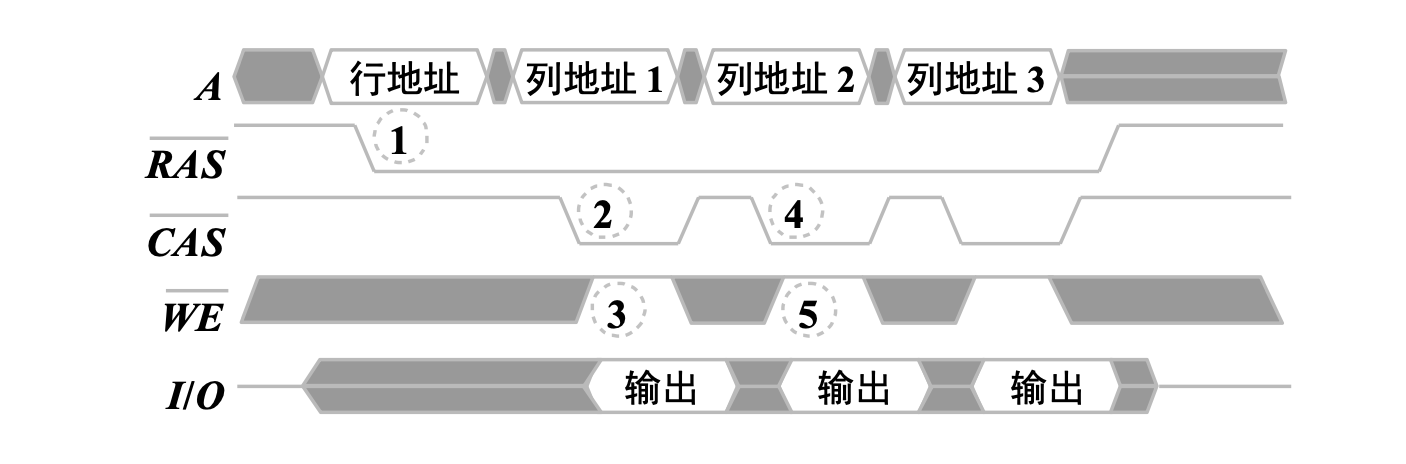

页模式操作:行地址不 变,只变列地址,有效提高连续地址读写速度

行刷新操作:一次刷新 指定行的所有单元

4. 存储器容量拓展

系统内存一般是由多个 RAM 芯片扩展而成的

存储容量的扩展

- 字长扩展(为扩展),通常 RAM 芯片字长为 1、4、8、16 和 32 位,当涉及的存储器位数超过 RAM 芯片字长时,要进行位扩展。

- 字数扩展,当 RAM 芯片的存储容量达不到设计存储器容量要求时,要用多个 RAM 芯片进行字数扩展。

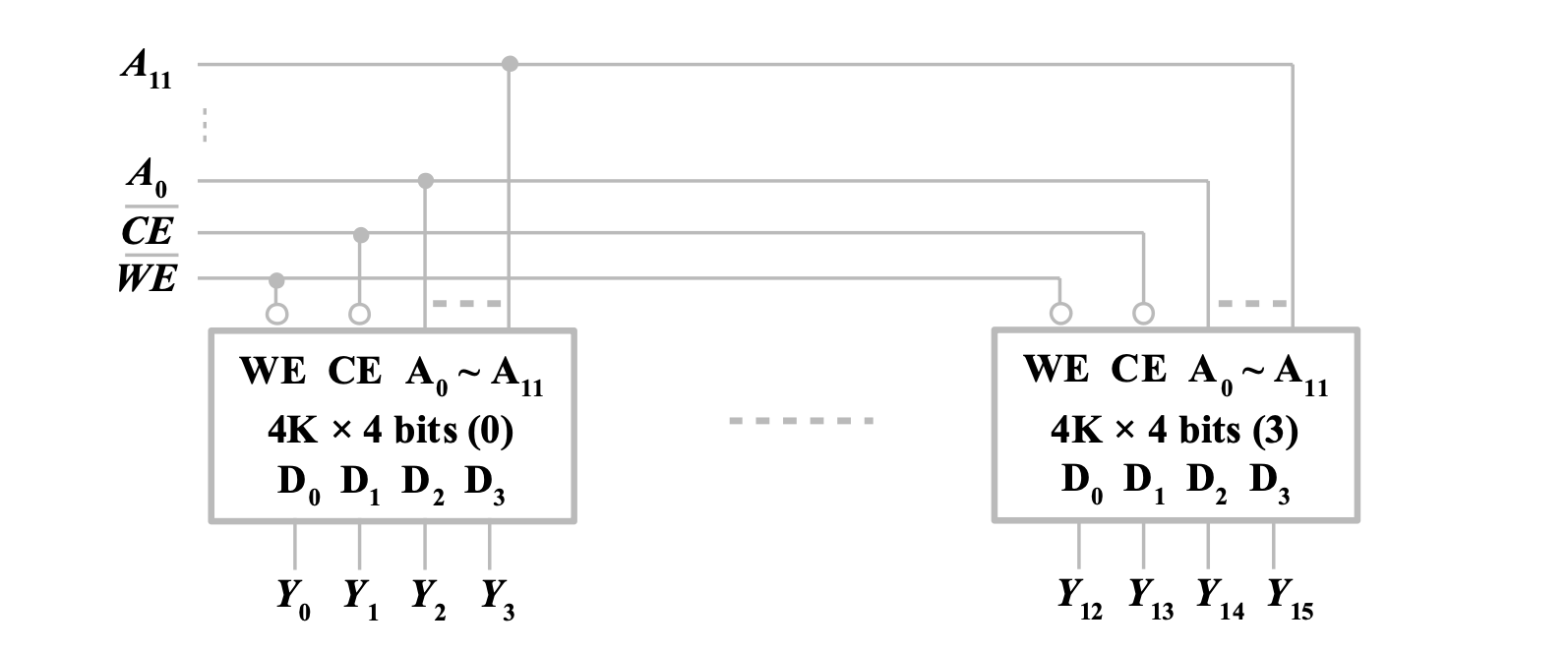

4.1 字长的扩展

字长扩展可采用并联的方式实现,即将 RAM 芯片的地址线、读写控制线和片选信号线对应的并联在一起,而各个芯片的输入/输出端作为字的各位。如用 4K × 4 位的 4 片芯片组成 4K × 16 位的存储系统

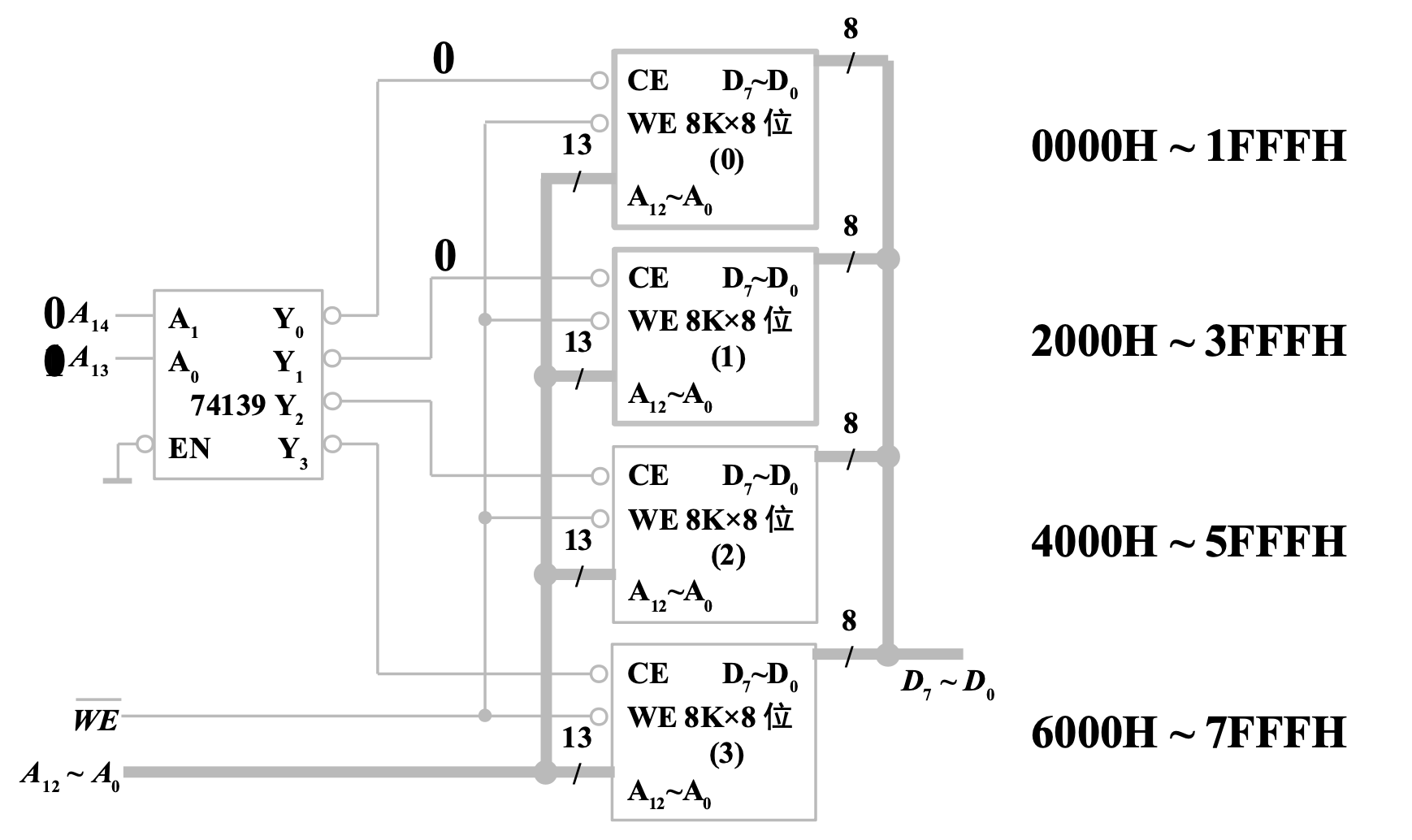

4.2 字数扩展

字数扩展即存储单元的扩展,利用外加译码器控制存储器芯片的片选使能输入端实现,要使各芯片的存储单元地址连续

例:用 8K × 8 位的芯片组成 32K × 8 位的存储系统

- 8K×8芯片:存储单元

- 32K×8存储系统:存储单元

利用外加译码器对

芯片地址范围确定方法

片选信号确定后,保持片选地址不变,取芯片的地址最小和最大,就 确定了该芯片的地址范围

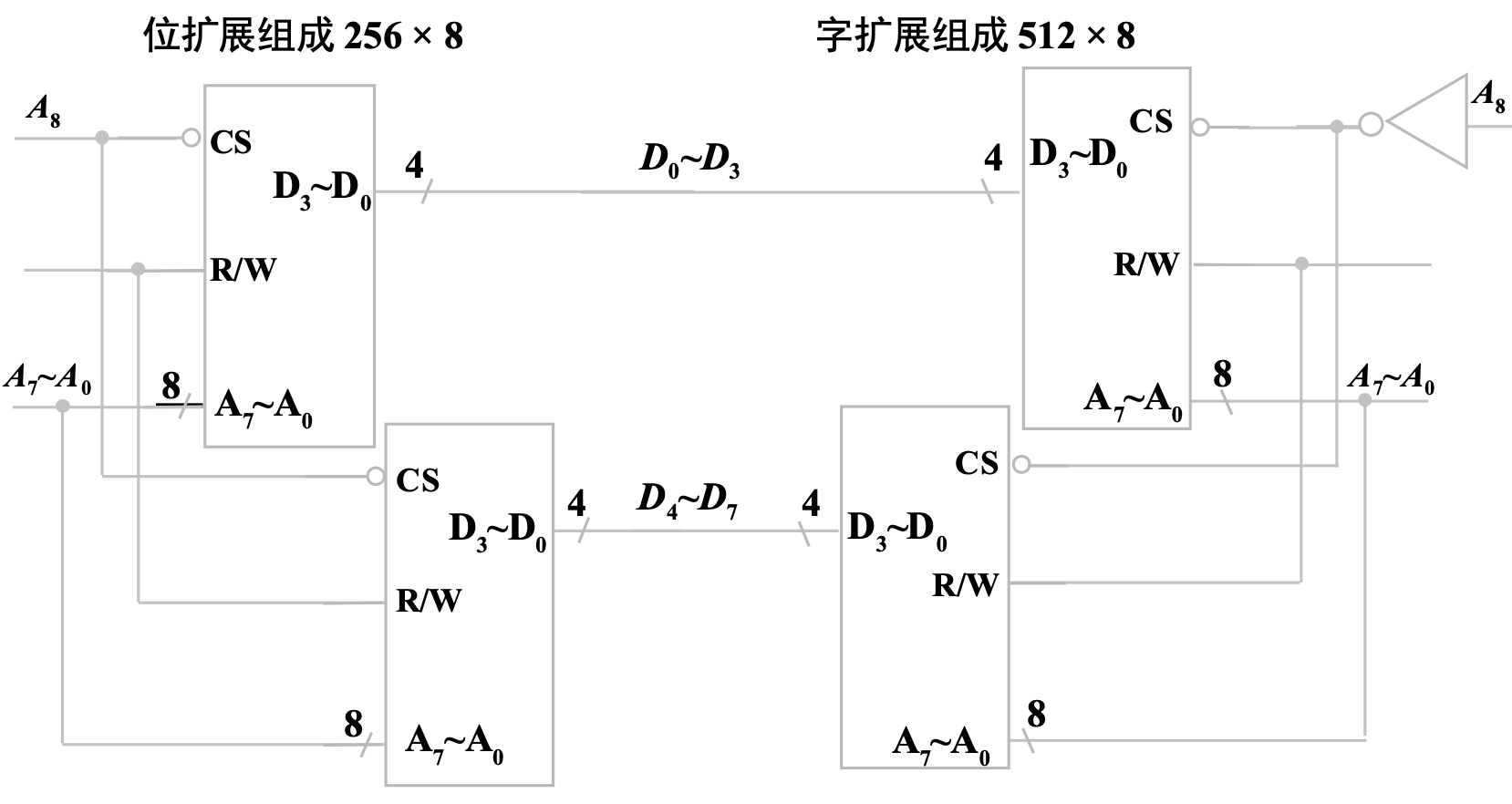

4.3 同时实现字数、位数的扩展

使用 256 × 4 位芯片组成 512 × 8 位存储器,问需要多少芯片 ? 电路应如何连接?